SSD: Cos'è e come funziona? [guida completa]

20 agosto 2021

1629449488000

Una guida per capire al meglio tutti gli aspetti degli SSD, dalle componenti al funzionamento pratico!

Subito dopo la guida sulle memorie RAM, con un occhio di riguardo su che cosa siano e come funzionino, è il turno degli SSD. Questa guida contiene vita, morte e miracoli dei Solid State Drive, quindi in certi campi bisogna addentrarsi nel tecnico, specialmente nella parte hardware. Cercheremo comunque di farlo senza rendere le cose troppo difficili.

Qui sotto troviamo un sacco di articoli e guide collegati/e al mondo degli SSD:

- COSA SONO E COSA CAMBIA TRA I VARI TIPI DI NAND FLASH (SSD);

- MIGLIORI SSD SATA (2021);

- MIGLIORI SSD NVME PCIE 3.0 E 4.0 PER GAMING E PRODUTTIVITÀ (2021);

- I MIGLIORI SSD PORTATILI SOTTO I 200€;

- DIFFERENZE TRA I TIPI DI SSD;

- PERCHÉ GLI SSD HANNO MENO SPAZIO DEL DICHIARATO?;

- COME SCEGLIERE UN SSD;

- TEMPERATURE SSD: COME GESTIRLE.

# Breve storia dei Solid State Drive (SSD)

“SSD” è l’acronimo di “Solid State Drive” ed è un dispositivo di memoria basato su semiconduttori e su memorie NAND Flash per archiviare i dati. All’inizio gli SSD non erano basati su NAND Flash come lo sono gli attuali, ma bensì su RAM. Infatti il primo SSD fu rilasciato nel 1976, prodotto da Dataram, con il nome “Bulk Core”. Questo SSD, con i suoi 2 MB di capacità, era compatibile con Equipment Corporation (DEC) and Data General (DG) computer. Dopo il Bulk Core il trend di usare la RAM rimase in auge finché SanDisk nel 1991 non decise di creare il primo SSD con NAND Flash: un prototipo OEM da 20 MB in configurazione PCMCIA venduto in un’asta per 1000$. Questo fu usato in un portatile ThinkPad da IBM. In seguito nel 1998 SanDisk decise di sfornare SSD in form factor 2½ e 3½ con un’interfaccia PATA (Parallel ATA, ora sostituita dalla SATA, Serial ATA).

# Com’è composto un SSD

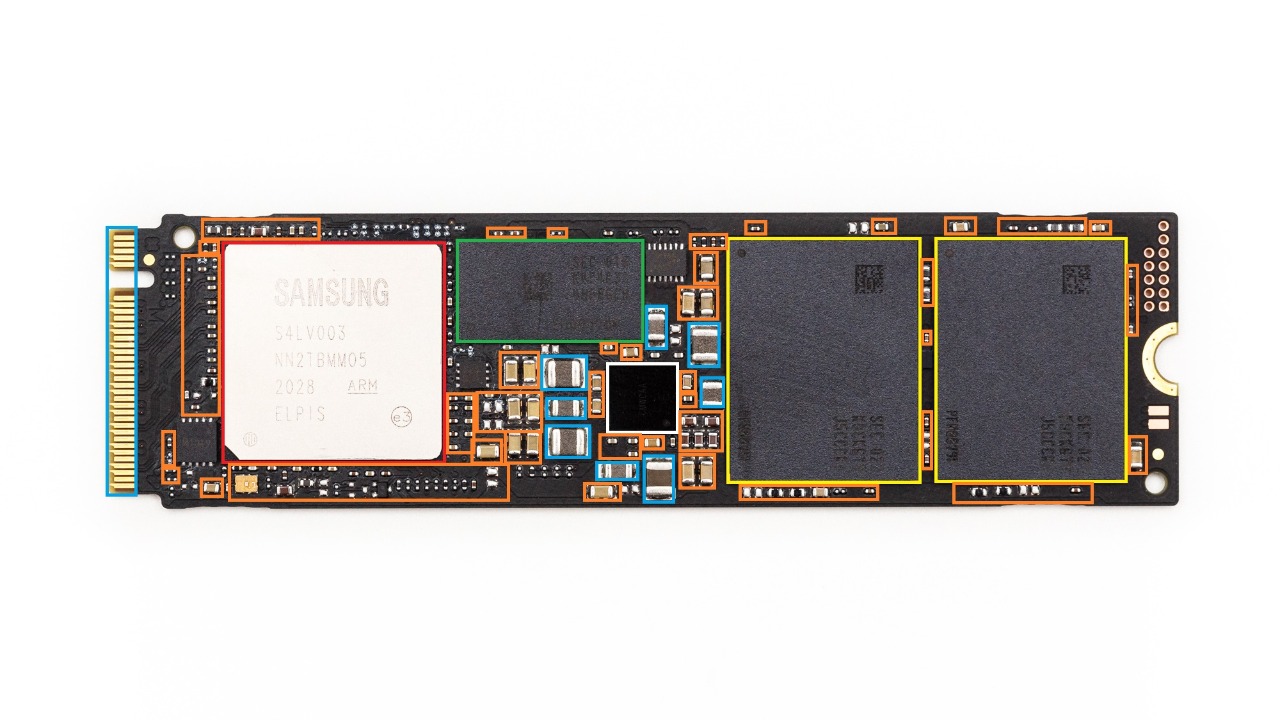

Un SSD è composto da diverse componenti, principalmente:

- Controller (rosso);

- NAND Flash (giallo);

- DRAM cache, presente in base al modello (verde);

- Condensatori (arancione), resistenze (arancione) e induttori (blu);

- PMIC (bianco);

- PCB (Printed Circuit Board);

- Interfaccia (blu a sinistra).

Composizione di un SSD in pezzi. Fonte: Tom's Hardware

Ognuna di queste componenti ha una propria funzione e la loro sinergia è in grado di far funzionare l’intero SSD.

# Controller

# Cos’è e come funziona?

Il controller è assimilabile al cervello dell’intero SSD, perché gestisce tutto quello che avviene a bordo. La funzione principale del controller è quella di trasferire la FTL (Flash Interface Layer) nelle NAND Flash, o nell’eventuale DRAM cache, per poi creare le funzioni che la FTL elenca. La FTL è come una mappa con sopra riportate tutte le funzioni che il controller deve svolgere: operazioni di scrittura, gestione dello S.M.A.R.T., ECC e altro. Più è veloce la FTL e più è veloce l’intero SSD, per questo la DRAM cache porta vantaggi in termini di prestazioni.

# Chi produce i controller degli SSD?

Attualmente sono diversi i produttori di controller: Samsung, WD e SanDisk producono in casa e non vendono a terze parti. Invece Phison, Silicon Motion, Marvell, InnoGrit, Starblaze, Maxiotek e Realtek producono in casa e vendono a terze parti.

- Phison è molto conosciuta per gli NVMe e i SATA di fascia bassa, quanto su 4.0.

- Silicon Motion per gli SSD SATA di fascia bassa e alta.

- Marvell ai tempi ha lavorato molto con Crucial sulla fascia “M” (MX300, MX200, M500, ecc.), perché prima dell’arrivo del SM2258 (Silicon Motion) Marvell disponeva dei migliori controller per la fascia alta.

- InnoGrit è nota per NVMe 4.0 di fascia alta e bassa (ADATA Gammix S70, Patriot Viper VP4300, Lexar NM620, ecc.),.

- Starblaze da Asgard per soluzioni NVMe 3.0 (AN3+), e Realtek è conosciuta per principalmente gli SSD SATA di ADATA e gli NVMe 3.0 di fascia bassa sempre di ADATA.

Prima c’erano meno produttori, e alcuni tutt’ora rimarchiano i loro prodotti: per esempio Lexar da InnoGrit sul modello NM620. Il leader dei controller all’inizio era SandForce: azienda purtroppo fallita dopo un po’.

# Architettura, core, canali e cle

Il controller è un microprocessore solitamente costruito sull’architettura ARM Cortex, anche se ci sono casi di ARC (Argonaut RISC Core, esempio col SM2258). Sono basati su un’architettura da 32-bit e le più famose sono la R4 (vecchi controller Samsung sui SATA, fino alla serie 860), la R5 (tutt’ora molto utilizzata, sia per i SATA che per gli NVMe) e la R8 (attualmente disponibile solo sul SM2264 di Silicon Motion, anche se non ancora in commercio come controller). Scegliere una determinata architettura può portare dei vantaggi come degli svantaggi

Ad esempio usare l’architettura ARM Cortex-R8 porta a performance generali migliori, ma anche consumi maggiori ed efficienza peggiore (motivo per cui il Phison E18 è ancora ARM Cortex-R5).

Essendo dei microprocessori anche loro hanno un numero di core: con alcuni casi in cui abbiano dei core aggiuntivi di un’altra architettura; per esempio il controller del Crucial P5 è il Micron DM01B2 e ha 4 core di tipo ARM Cortex-M3 insieme a due ARM Cortex-R5 che lavorano a una frequenza più alta. Phison utilizza i CoXProcessor nei suoi controller per NVMe, che sarebbero una coppia di ARM Cortex-R5 solo a una frequenza più bassa rispetto agli altri (non appartenenti ai CoXProcessor). Per fare un esempio, il Phison E13T è un controller per NVMe che ha un core ARM Cortex-R5 da 667 MHz con un CoXProcessor, quindi in totale ha tre core ARM Cortex-R5 sebbene i due ARM Cortex-R5 nel CoXProcessor abbiano una frequenza minore.

I core a loro volta hanno un numero di canali di gestione delle NAND, ovvero i canali con cui il controller è in grado di comunicare con le NAND (per la gestione della DRAM serve un controller apposito installato nel controller stesso). Ogni canale contiene i propri pin del segnale di controllo per indicare il tipo di dati o comandi che si trovano sul bus, infatti per comunicare con le NAND si utilizza un bus con un’interfaccia di tipo bidirezionale (DQ usando il DQS, ovvero il segnale di strobe) con un segnale di clock continuo e con vari ingressi e uscite. Il bus include l’address latch enable (ALE) che serve per segnalare che il controller stia inviando un indirizzo e il command latch enable (CLE) che serve per segnalare che il controller stia inviando un “comando flash”. Ogni fronte di salita del write enable (WE) indica che la NAND Flash dovrebbe scrivere la parte di dati attualmente inviato sul bus dal controller dell’SSD. Allo stesso modo ogni fronte di salita del segnale di read enable (RE) indica che la NAND Flash debba inviare la successiva parte di dati verso il controller dell’SSD.

I canali del controller degli SSD dispongono di una determinata velocità, e se questa velocità dovesse essere in contrasto con quella delle NAND perché troppo bassa, si incorrerà in un collo di bottiglia/bottleneck da parte del controller. Per fare un esempio: ci sono casi di SSD con il controller Silicon Motion SM2263 e con delle NAND 96L. I 4 canali dell’SM2263 sono da 667 MT/s, ma le 96L solitamente da 800 MT/s: l’SM2263 sta limitando le velocità delle NAND, quindi dell’intero SSD. Infatti in questo caso, per sfruttare al massimo la velocità delle NAND servirebbe un controller come un SM2262, che ha 8 canali da 800 MT/s.

Se parliamo di canali dobbiamo parlare anche delle CE, ovveri i “chip enable”, che tradotto in italiano sta per “abilitazione chip”. Ogni die delle NAND Flash ha il proprio segnale CE, che serve per selezionare i die con cui si vuole far avvenire la comunicazione tramite canali. Quindi, i CE indicano il numero massimo di die delle NAND Flash con cui possono “comunicare” per canale (o in totale, dipende da come viene espresso). Per esempio, se un controller da 8 canali ha in totale 32 CE, vuol dire che ogni canale avrà 4 CE (32/8 = 4), quindi vuol dire che ogni canale può “comunicare” con un massimo di 4 die in una NAND Flash. Attualmente il numero più alto di CE registrati è 64 sul Silicon Motion SM2264 (rispettivo competitore del Phison E18), che è riuscito ad arrivare a questo numero davvero elevato grazie all’uso dell’architettura ARM Cortex-R8. Se fosse basato sull’ARM Cortex-R5 probabilmente non ce l’avrebbe fatta e sarebbe stato da 32 come la stragrande maggioranza di tutti i controller attuali (anche perché l’SM2264 è attualmente l’unico controller basato su ARM Cortex-R8 negli SSD di fascia consumer).

# ECC

Ogni controller ha un proprio ECC (Error Correction Code) che solitamente è di due tipi: BCH (Bose–Chaudhuri–Hocquenghem codes) o LDPC (Low-density parity-check code). Il BCH è più vecchio e meno performante dell’LDPC (allo stesso tempo meno usato), e l’LDPC è ormai presente in tutti i controller moderni. Si può pensare che l’ECC rientri in un processo decisionale “hard” o “soft”. La decodifica “hard” è più “debole” ma è semplice da implementare, mentre la decodifica “soft” è più complessa ma porta risultati migliori e allo stesso tempo richieste di prestazioni da parte del controller maggiori. Mentre l’ECC di tipo BCH può fare solo il primo (hard), l’LDPC può fare entrambi (hard e soft), il che migliora la sua abilità di “fuzzy” dei dati dalle celle (NAND Flash) con una potenziale maggiore latenza di lettura. Generalmente con l’LDPC si effettuerà prima la decodifica hard e solo in caso di fallimento (dell’hard) verrà utilizzata la decodifica soft; infatti per questo l’LDPC è migliore del BCH come prestazioni. Inoltre, con la decodifica soft si utilizza il rilevamento progressivo, ovvero livelli di rilevamento extra che se necessario determinano il valore dei dati scambiando solo prestazioni peggiori quando necessario. Questo è anche noto come “LDPC a più fasi”. A causa dello sviluppo di controller più veloci ed efficienti, l’LDPC tende a portare il miglior equilibrio. Se l’intero ECC dovesse fallire la risoluzione i dati possono essere recuperati tramite un altro processo, ma non stiamo qui ad approfondire visto che è un concetto lungo e complesso.

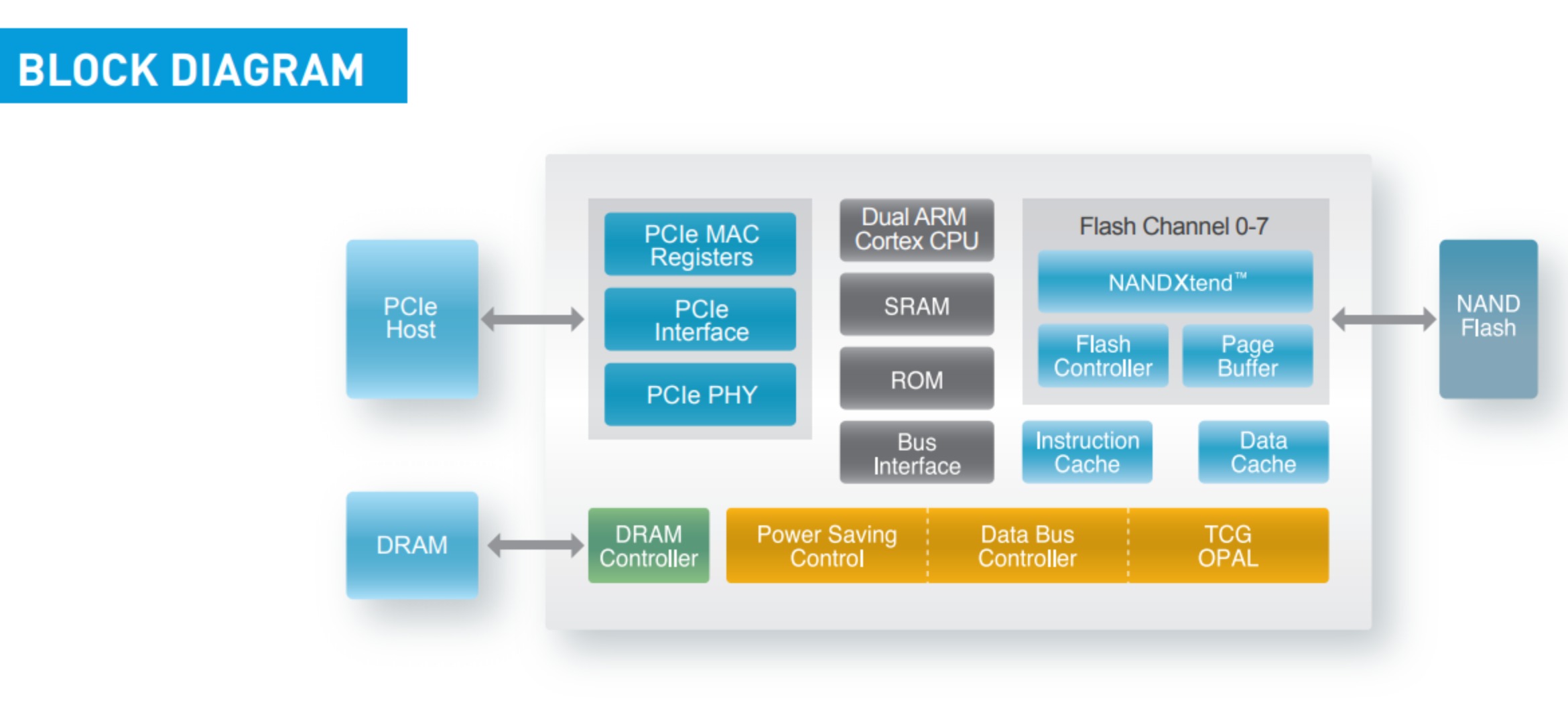

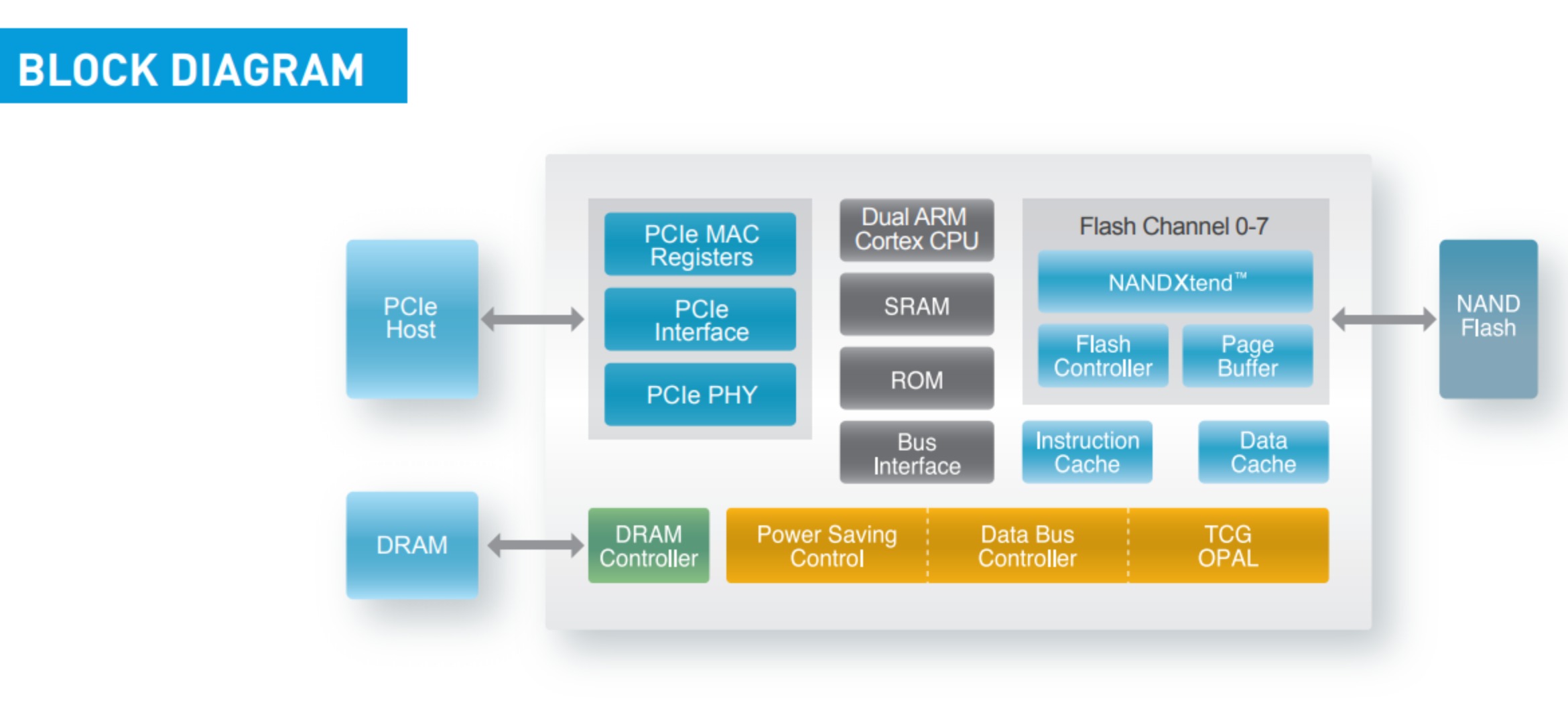

Qui un esempio di architettura in una diagramma a blocchi di un controller; in questo caso l’SM2262EN:

Fonte: Silicon Motion

# Nand flash

Abbiamo già parlato in parte delle NAND Flash in un altro articolo (COSA SONO E COSA CAMBIA TRA I VARI TIPI DI NAND FLASH (SSD)) dove si focalizzava principalmente sulle “versioni” (SLC, MLC, TLC, QLC), ma adesso entreremo di più nel profondo per capire filo per segno cosa sono, come organizzano i dati e l’importanza che hanno al giorno d’oggi nel mondo dell’archiviazione.

# Cosa sono

Le NAND Flash sono delle memorie di tipo non-volatile, ovvero che sono in grado di mantenere i dati senza carica elettrica per un determinato periodo, e quindi l’opposto dei chip DRAM nelle RAM che sono di tipo volatile. È da anni che ormai si utilizzano le NAND Flash negli SSD (anche nelle USB, micro SD, SD, ecc.). Come abbiamo già detto prima gli SSD si basavano solo sui chip DRAM, mentre ora sulle NAND Flash. Le si utilizzeranno ancora per molto, poiché in questi tipo di dischi sono quelle più adatte, grazie ai buoni rapporti di qualità/prezzo.

Nel lontano 2017, in una presentazione dell’FMS (Flash Memory Summit), Peter W. Lee, attuale BDO (al tempo CEO) di APlus Flash Technology fece una proposta e una presentazione riguardo un tipo di NAND sostitutive alle NAND Flash “normali”: le “AI-NAND” o “HiNAND”. Questo tipo di NAND sono pensate per raggiungere le prestazioni delle SCM (3D XPoint, MRAM, ReRAM) abbattendo i costi. Le AI-NAND sarebbero state più veloci delle NAND (e di molto) visto che possono - sul piano teorico - eseguire più J-Tasks per piano (le NAND ne fanno 1 una per piano) e perché sono essenzialmente composte da DRAM (Fast Front-end) e NAND (Low-cost Back-end), ma purtroppo non sono state prese in considerazione più di tanto visti i numerosi problemi di cui soffrono.

# Come sono fatte

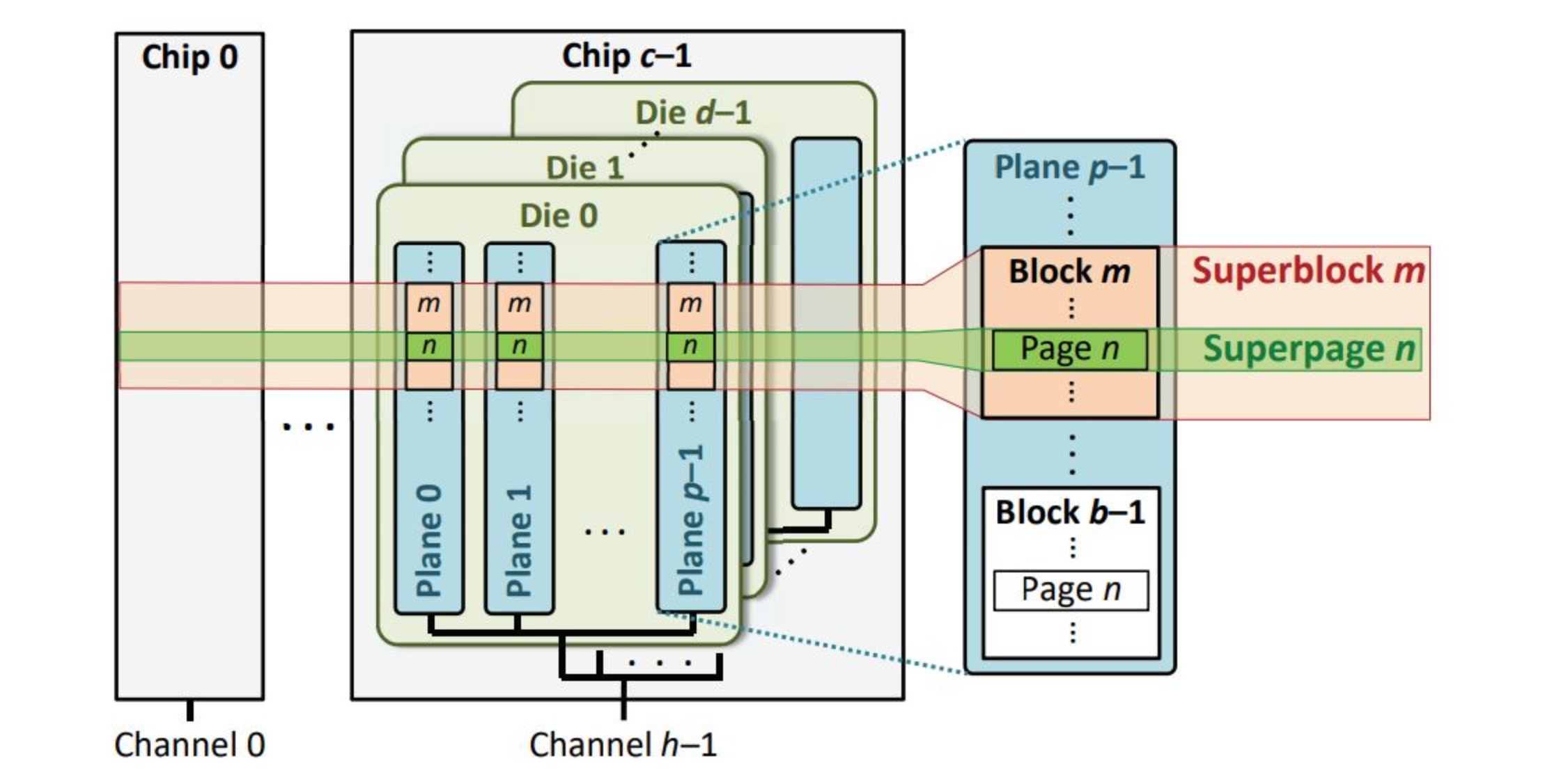

Qui una rappresentazione dell’organizzazione interna di una NAND Flash:

Fonte: "Errors in Flash-Memory-Based Solid-State Drives: Analysis, Mitigation, and Recovery"

Qui una rappresentazione di una NAND Flash da 96L in 3D:

Fonte: Semiconductor Engineering

Una NAND è formata in questa sequenza:

- Package (o in italiano “pacchetto”) o “chip”:

Il chip della NAND Flash è ciò che vediamo fisicamente. Questi chip sono costituiti da uno o più die, con generalmente un massimo di sedici (“16DQ” o “HDQ”) per esadecimale. Le “pile” con più die sono più difficili da gestire a causa di rese e altri fattori. Una NAND di tipo TLC 64L con densità di 256Gb (Gigabit) per die avrà 32-512 GiB (Gibibyte) di flash per l’archiviazione di dati. Il package può essere di due tipi: TSOP (Thin small outline package) o BGA (ball grid array), le NAND con il package di tipo TSOP sono ormai obsolete e più facili da “rimuovere” durante un “chip-off” (una tecnica che viene eseguita nel recupero dati “rimuovendo” fisicamente i chip dal PCB), le BGA sono quelle che sono in produzione tutt’ora e non hanno pin “esterni”.

Esistono diversi modi per impilare i die in un chip NAND, sebbene l’alternanza di ogni quattro die in uno schema a scala/a cascata sia il metodo predefinito. Questa struttura complessiva è nota come “package-in-package” o “package-on-package” che in italiano sta per “pacchetto nel pacchetto” o “pacchetto nel pacchetto”.

Nella prima figura, i chip vengono mostrati come “Chip 0” e “Chip c-1”.

- Die:

Un singolo die di una NAND può avere 8 o 16 pin per la comunicazione I/O in relazione alla modalità da 8, 16 o doppio 8-bit (attualmente il più comune è l’8-bit o 1 byte). Può avere una quantità variabile di flash, il più comune è 256 Gb o 512 Gb per die con NAND di tipo TLC e 1 Tb per die con NAND di tipo QLC - 32 o 64 GiB per die o 128 GiB per die. Ogni die avrà più piani a cui è possibile accedere, di solito due o quattro con le attuali NAND Flash. La densità del flash può influire sulle prestazioni in base alla quantità di canali del controller e alla capacità di interleaving.

Nella prima figura, i die vengono mostrati come “Die d-1”, “Die 1” e “Die 0”.

- Piani:

Ogni piano può contenere migliaia di blocchi. Un normale piano in una NAND 64L TLC sarebbe 16GiB, o metà della capacità totale (die a due piani). È possibile accedere ai piani in modo indipendente fornendo il doppio (o più) della larghezza di banda. Ogni piano avrà uno o più registri delle dimensioni di una pagina, ad esempio i registri dei dati e della cache (DL, XL) per il trasferimento dei dati tra le NAND Flash e il controller (per esempio “page buffer”) o per il “buffering” dei bit durante la programmazione. Da notare che alcune NAND possono avere una struttura a “tile” (ad esempio le NAND 3D di Micron/Intel) con piani virtuali con altre configurazioni che coinvolgono i circuiti periferici dell’intera NAND.

Nella prima figura, i piani vengono mostrati come “Plane 0”, “Plane 1” e “Plane p-1”.

- Sottopiani:

Una divisione di un piano in due o più piani con ciascuno la propria circuiteria (ad esempio il buffer di pagina) e che possono migliorare le prestazioni di interleaving. Ad esempio, una tipica pagina/wordline da 16 KB in un piano potrebbe essere divisa in due “linee” da 8 KB con due sottopiani, migliorando le letture più piccole. Con le NAND Flash IMFT (Micron/Intel) i sottopiani sfruttano l’architettura “tile” da 2 KB (coppie di 4 KB) per migliorare (esempio) le letture parziali, nonostante anche altre architetture possano utilizzare i tile o un altro tipo di struttura. I sottopiani sono usati nelle NAND di Samsung di sesta generazione (le 128L), infatti hanno due piani “normali” e due sottopiani, per un totale di 4.

- Superblocchi:

Dei “gruppi” di blocchi su tutti i piani che hanno lo stesso identificatore (ID) o offset. Il controller accederà a un superblocco vuoto alla volta.

Nella prima figura, i superblocchi vengono mostrati come “Superblock m”.

- Blocchi:

Ogni blocco può contenere centinaia di righe di celle flash. I blocchi attuali hanno solitamente una dimensione di 24 MB, anche se le QLC hanno blocchi di dimensioni maggiori rispetto alle TLC. Questa è l’unità più piccola cancellabile in una NAND Flash. Da quest’ultima si può eseguire anche una cancellazione parziale del blocco con le giuste circostanze.

Nella prima figura, i blocchi vengono mostrati come “Block m” e “Block b-1”.

- Sottoblocchi:

Dei blocchi che possono essere cancellati parzialmente, per esempio a metà. Un blocco può avere due o più sottoblocchi, ma questa tende ad essere una configurazione “speciale”, infatti è tutt’ora molto poco diffusa, se non ancora inesistente. Un motivo per cui adottare una struttura a sottoblocchi in una NAND Flash è nel migliorare la comprensione dei circuiti sottostanti della NAND Flash.

- Superpagine:

Dei “gruppi” di tutte le pagine di un superblocco con lo stesso ID o offset. Il controller scriverà una superpagina vuota alla volta per le massime prestazioni e massima efficienza sfruttando il parallelismo.

Nella prima figura, le superpagine vengono mostrate come “Superpage n”.

- Pagine:

Le pagine sono le unità più piccole che possono essere scritte in un SSD e sono una serie di bit con una dimensione tipica di 16 KB in una moderna TLC. Una NAND con più di un bit per cella (MLC) avrà una pagine “forte” (il primo bit programmato) e una pagine “debole” (bit successivi) con diverse conseguenze correlate. Da notare che è possibile scrivere a livello di sottopagina ma con un’affidabilità molto più ridotta.

Nella prima figura, le pagine vengono mostrate come “Page n”.

- Sottopagine:

Man mano che le dimensioni delle pagine crescono, c’è una maggiore disparità tra le dimensioni della pagina, per esempio 16 KB per le TLC tipiche (con qualsiasi numero di layer) e le dimensioni del settore o del cluster, ad esesempio 512 B e 4 KB rispettivamente. Una pagina fisica di 16 KB può quindi essere suddivisa in quattro sottopagine o quattro pagine logiche da 4 KB ciascuna. Si lavora con le tabelle di indirizzamento solitamente a livello di pagina, ma possono essere a più livelli per indicizzare sottopagine. Gli SSD possono anche eseguire letture parziali (dell’intera pagina da 16 KB) a livello di sottopagina.

- Wordline:

Una riga di celle in cui i dati possono essere scritti. Ogni riga di bit delle celle all’interno di una wordline (o “word line” o “word-line”) forma una singola pagina. Quindi, le TLC che contengono massimo 3 bit per cella, contengono fino a 3 pagine di dati per pagina. I bit sono posizionati dai valori minimi ai più significativi (LSB, MSB) che influenzano il modo in cui i dati vengono scritti attraverso gli impulsi di tensione. In modalità SLC (o pSLC) viene utilizzatafloating gate solo una riga di bit o una riga di pagine di una wordline, migliorando le prestazioni al costo della capacità della cella, sebbene sia a livello di blocco.

Da notare che il numero di layer delle NAND indica il numero totale di wordline e celle della NAND; quindi se una NAND è da 64L vuol dire che ha 64 wordline. C’è anche da dire che il numero totale dei layer è sempre maggiore rispetto a quello espresso: per fare un esempio, le 64L Micron TLC sono in realtà da 74 layer con 66 layer di flash. In questo caso però 2 di questi sono SLC 2 sono MLC, quindi effettivamente ci sono 64 wordline e celle TLC. Oppure, per fare un altro esempio, le 92L Samsung utilizzate sul 970 EVO sono in realtà da 100 layer perché 8 di questi sono dummy wordline. Attualmente il numero massimo di layer registrato è 176L con le Samsung di settima generazione, le SK Hynix anche loro di settima generazione, le Micron B47R e le Kioxia BiCS6. Ci sono anche le 128L (Micron B37R, Kioxia BiCS5, Samsung e SK Hynix di sesta generazione). Le più diffuse attualmente sono le 64L e 96L. Le NAND 2D non hanno un numero di layer dato che non sono verticali come le NAND 3D.

Tra le 64L, 92L/96L, 128L e 176L c’è anche una differenza in termini di performance: solitamente, le 64L sono da 533 o 667 MT/s, le 92L/96L da 800 MT/s, le 128L da 1200 MT/s e le 176L da 1600 MT/s. Come unità di misura si utilizzano i megatransfer al secondo per il motivo che le NAND lavorano in DDR (Double Data Rate), infatti se una NAND ha una velocità di trasferimento dati da 800 MT/s vuol dire che la frequenza del clock è di 400 MHz. Tuttavia c’è da dire che la velocità crescente dei MT/s non dimostra la larghezza di banda effettiva ma riflette la capacità della NAND Flash di eseguire interleaving in modo più efficiente per velocità di trasferimento più elevate dato che sono limitate dalla velocità del bus del controller per canale, quindi i MT/s non riflettono completamente la loro velocità, diciamo.

Anche se c’è differenza in termini di velocità tra determinato numero di layer e un altro, non sempre c’è però un salto in affidabilità, dipende dai casi specifici: per esempio tra le Intel QLC da 64L e 96L c’è differenza perché c’è un gran cambiamento come densità del die, anche se entrambi i die in questo caso sono da 1Tb (6.53mm² per le 64L e 8.9mm² per le 96L).

Nella seconda figura, le wordline vengono mostrate come “Word line: Metal fill”.

- Bitline:

Le wordline sono disposte in colonne note come “bitline”. Il totale di queste bitline forma un intero blocco. Due approcci sono usati per programmare le bitline: “shielded bitline (SBL)” con bitline pari/dispari o “all-bitline (ABL)” con diversi vantaggi e svantaggi. per esempio, l’SBL è un po’ più veloce dell’ABL per la lettura delle sottopagine a causa di tempi di assestamento bitline inferiori. La manipolazione dei bitline adiacenti può influire sulle prestazioni e sulla resistenza.

Nella seconda figura, le bitline vengono mostrate come “Bit line: Metal fill”.

- Celle:

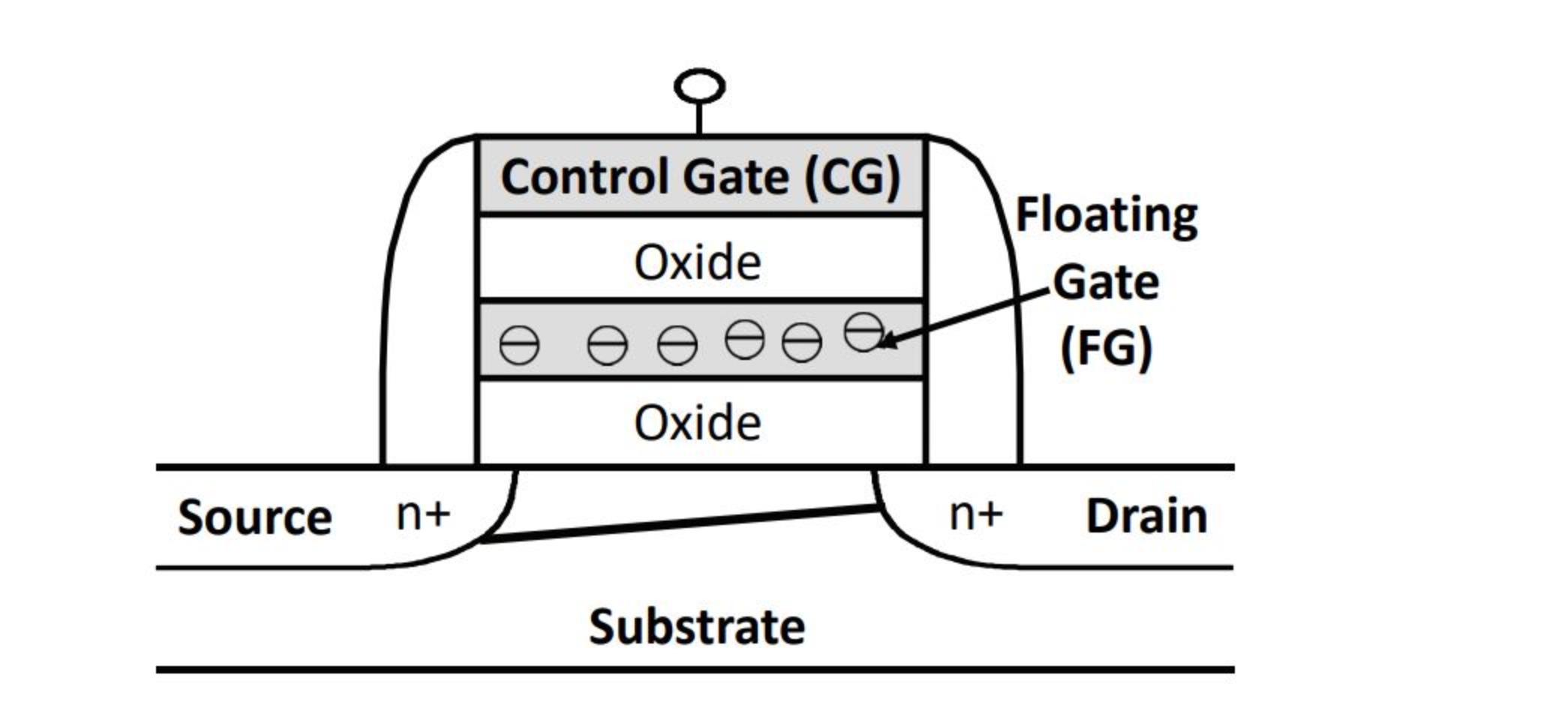

Le celle sono tra le componenti più importanti nella NAND Flash, perché archiviano i dati. (quando parliamo di floating gate (FG), charge trap flash (CTF), replacement gate (RG), ecc. intendiamo il “tipo” di cella). Il flash originariamente era disponibile in una disposizione a gate flottante, come nel MOSFET a gate flottante (FGMOS), costituito da un gate flottante isolato tra strati isolanti con un substrato e un gate di controllo (oltre a source e drain dei transistor tradizionali).

La cella all’inizio era disponibile solamente in un tipo: il floating gate; infatti questa tecnologia risale a davvero tanti anni fa e non è utilizzata solo in componenti come le NAND Flash. Come abbiamo già detto, la cella floating gate è caratterizzata da un MOSFET “particolare” perché al posto di avere un solo gate ne ha due. Esistono diversi tipi di floating gate, per esempio “3D Conventional FG (C-FG)” e “Dual Control-Gate with Surrounding Floating Gate (DC-SF)”. Questa tecnologia è stata utilizzata da molto tempo per Micron, ora con l’esordio delle 128+L l’ha completamente abbandonata (passando alla replacement gate) e la utilizza solamente Intel, seppure quest’ultima abbia venduto le sue NAND a SK Hynix per 9 miliardi.

Quindi, attualmente abbiamo la tecnologia floating gate che viene usata da Intel, la charge trap flash in BiCS che viene usata da WD/SanDisk/Kioxia/Toshiba, la charge trap flash in P-BiCS e SP-BiCS che viene usata da SK Hynix e la replacement gate su TCAT usata da Samsung e Micron. Ognuno di questa tecnologia usa dei determinati componenti che possono essere diversi dalle altre, per esempio le NAND charge trap flash non usano il floating gate. La scelta di usare una determinata tecnologia è influenzata dall’affidabilità, dalle prestazioni, dalla scalabilità, ecc. della NAND stessa.

Nella seconda figure, le celle vengono rappresentate come “Single memory cell”.

# Come le NAND Flash archiviano i dati

Per spiegare come archiviano i dati le NAND Flash prenderemo come esempio quelle con architettura floating gate. L’architettura floating gate è ad oggi utilizzata solo da Intel, ma in passato (fino alle 96L) anche da Micron. Ora Micron - da 128L in su - è passata all’architettura replacement gate su TCAT (sarebbe una charge trap flash “custom”, diciamo), Samsung ha sempre lavorato sulla replacement gate su TCAT, Kioxia/Western Digital/SanDisk/SK Hynix (Kioxia è il rebrand di Toshiba, SanDisk è proprietà di Western Digital ed entrambe producono NAND) su architettura charge trap flash basandosi su BiCS (T-BiCS, P-BiCS, DP-BiCS, ecc.) e YMTC (produttice sul mercato orientale) su charge trap flash.

Qui una rappresentazione di una NAND Flash con architettura floating gate:

Fonte: "Errors in Flash-Memory-Based Solid-State Drives: Analysis, Mitigation, and Recovery"

Come possiamo vedere assomiglia a un MOSFET. Infatti le NAND Flash sono basate sui transistor MOSFET (ovvero transistor a effetti di campo - FET - che utilizzano la tecnologia MOS), solamente che i MOSFET “normali” hanno solo un gate, questi due. Alla base di tutto c’è il silicio (“Substrate”), dove sono presenti gli elettroni; a sinistra (“Source”) e a destra (“Drain”) i due pin per far entrare e uscire la corrente con a fianco (i due “n+”) i loro due terminali; con “Oxide” vengono indicati i dielettrici che separano i vari gate tra di loro e il floating gate con il silicio, il “Floating Gate (FG)” sarebbe il gate che immagazzina gli elettroni e il “Control Gate (CG)” è il gate in cima alla cella e che, oltre a collegare la cella alle word line, invia un segnale al controller dicendo se sono presenti degli elettroni nel floating gate oppure no; ciò serve per indicare al controller se l’intera NAND è carica o no. Il valore “0” indica che ci sono elettroni e quindi che la NAND è carica, il valore “1” indica che non ci sono elettroni e quindi che la NAND non è carica. Funge diciamo da “I/O”. Gli elettroni per arrivare al floating gate devono eseguire l’effetto tunnel, ovvero creare un campo elettrico caricato negativamente che serve per “oltrepassare” il dieelettrico.

Il modo in cui vengono archiviati i dati (in bit) in una NAND floating gate è lo stesso per le NAND replacement gate su TCAT e charge trap flash “pure”, solo che tra di loro cambiano i componenti delle celle.

# Operazione di scrittura

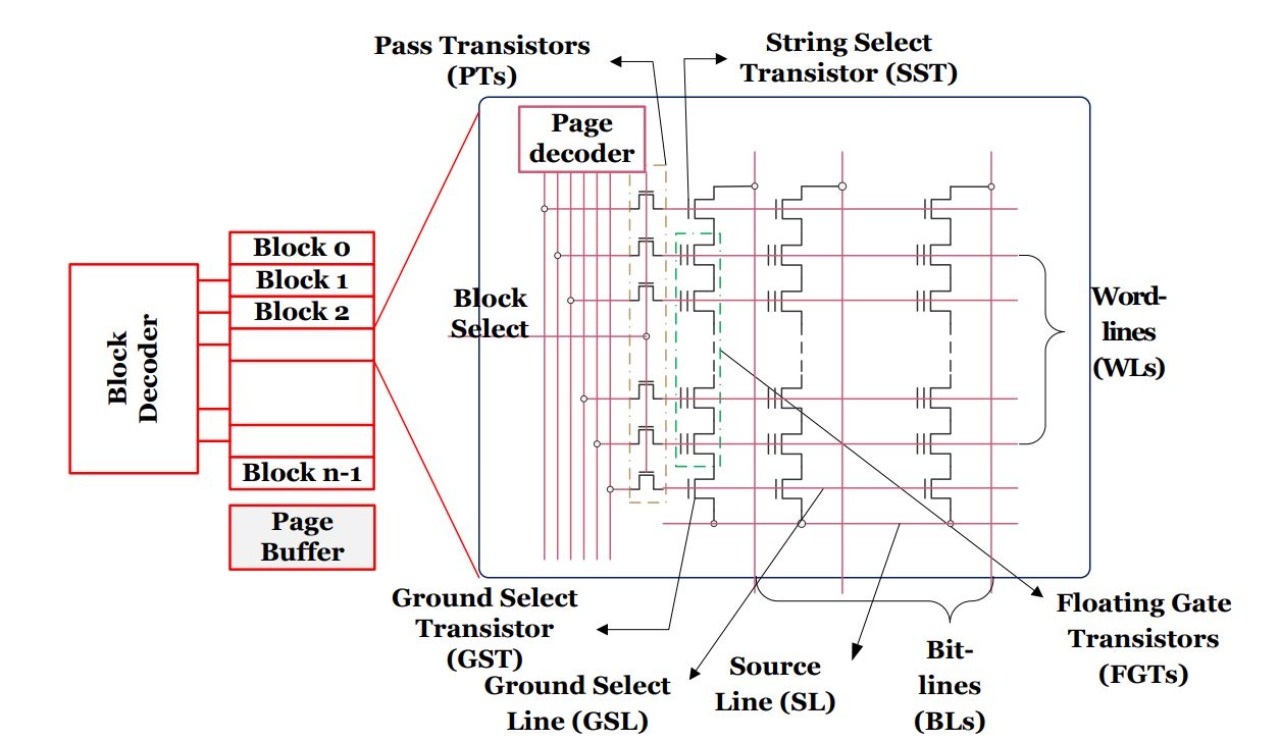

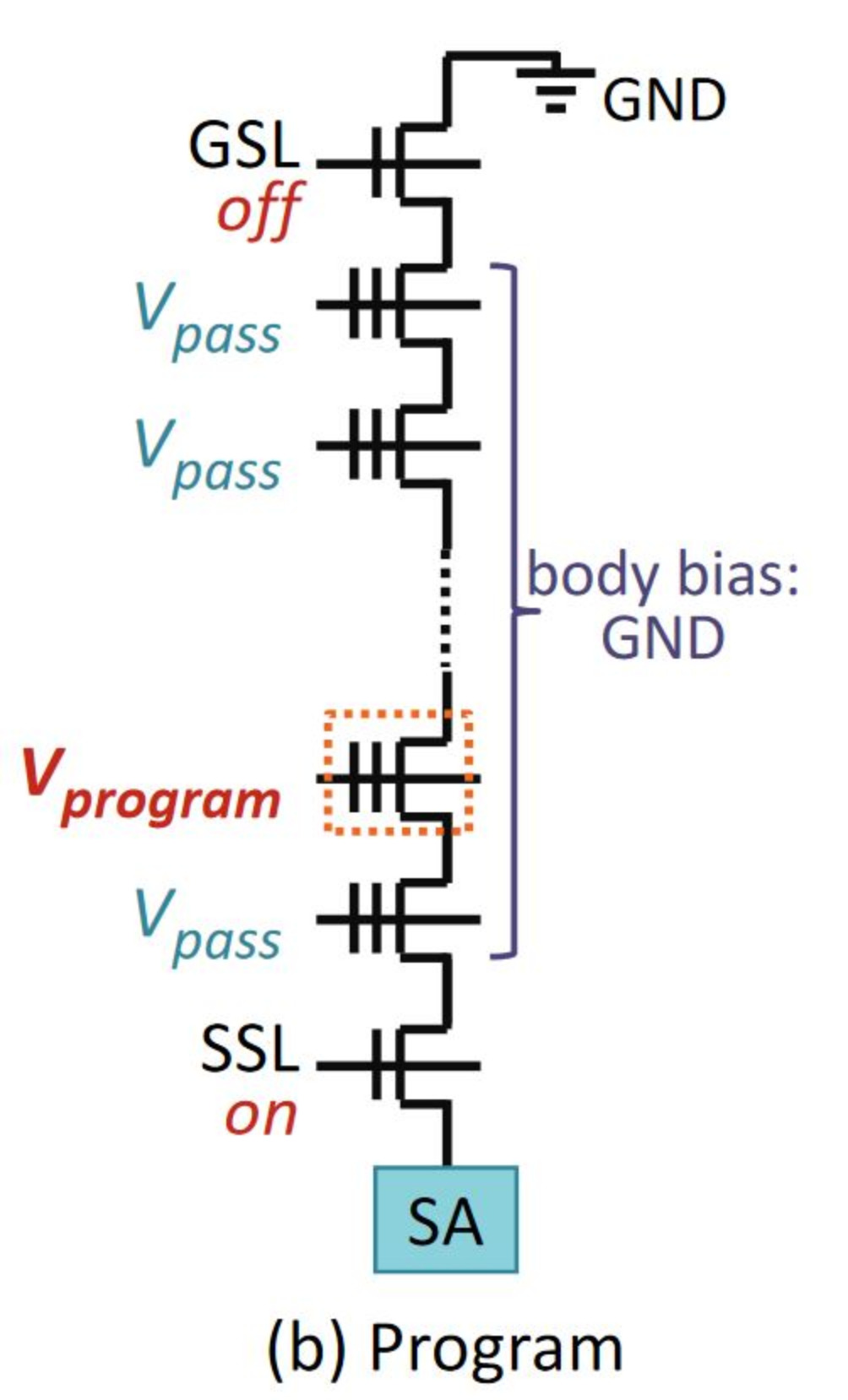

Organizzazione interna di un blocco - fonte: "MODELING THE PHYSICAL CHARACTERISTICS OF NAND FLASH MEMORY"

Per eseguire un’operazione di programmazione, ovvero scrivere “0” nelle celle desiderate, il controller dell’SSD deve determinare l’indirizzo fisico della pagina da programmare. Per ogni operazione di scrittura è necessario scegliere una pagina valida libera perché la memoria NAND Flash non consente l’operazione di sovrascritture sulla stessa pagina (come invece permettono di fare gli hard disk, per quanto quest’ultimi non abbiano pagine ma tracce). Il controller trasmette quindi alla NAND Flash il comando per la programmazione, i dati da programmare e l’indirizzo fisico della pagina. Quando dal controllor arriva una richiesta per un’operazione di programma viene selezionata una riga dell’array di memoria (corrispondente alla pagina richiesta) e i latch nel buffer di pagina vengono caricati con i dati da scrivere. L’SST (String Select Transistor) viene quindi attivato mentre il GST (Ground Select Line) viene disattivato dalla control unit. Affinché si verifichi l’effetto tunnel, è necessario un campo elettrico elevato posto il floating gate e il silicio come abbiamo già detto prima. Questo elevato campo elettrico si ottiene impostando il control gate della riga selezionata su un’alta tensione Vpgm e polarizzando le linee di bit corrispondenti allo “0” logico. Ciò crea un’elevata tensione tra il floating gate e il silicio, comportando il passaggio tra questi due. Per la programmazione logica “1” (che è sostanzialmente una non-programmazione), la cella di memoria dovrebbe rimanere nello stesso stato di prima dell’operazione di scrittura. Sebbene vengano adottate diverse tecniche per prevenire l’effetto tunnel degli elettroni per tali celle, assumiamo l’operazione di inibizione del programma auto-potenziato. Questa tecnica fornisce la necessaria tensione della programmazione di inibizione pilotando le bit line corrispondenti a “1” logico a Vcc e accendendo SSL e spegnendo GSL. Quando la word line della riga selezionata sale al Vpgm, la capacità in serie attraverso il control gate, il floating gate, il canale e il “bulk” vengono accoppiati, aumentando automaticamente il potenziale del canale e prevenendo l’effetto tunnel degli elettroni.

Fonte: "Errors in Flash-Memory-Based Solid-State Drives: Analysis, Mitigation, and Recovery"

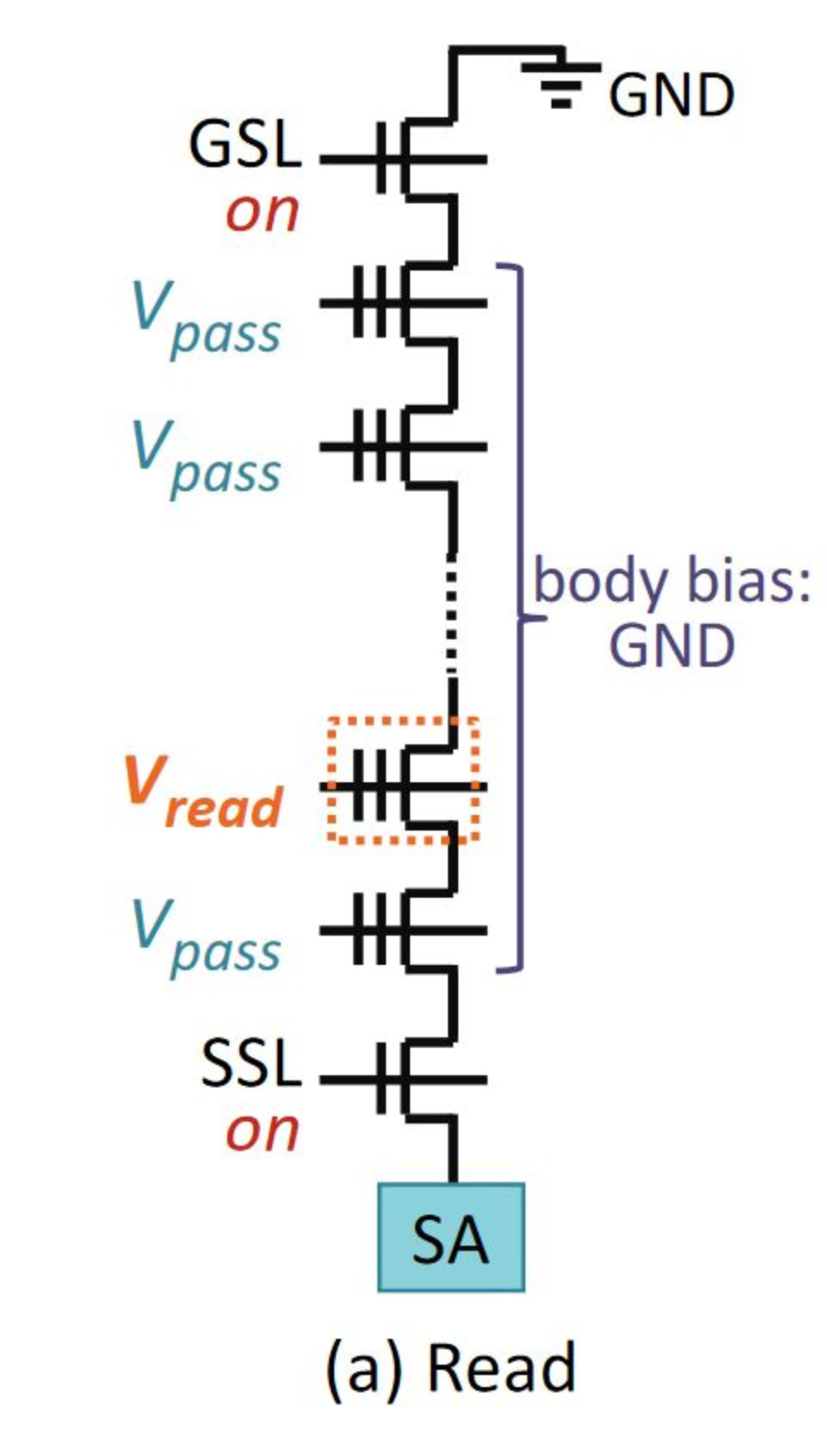

# Operazione di lettura

Per eseguire un’operazione di lettura, il controller determina l’indirizzo fisico della pagina da essere letto in base alla mappatura dell’indirizzo logico-fisico. Questo indirizzo viene poi passato alla “control unit” nel chip NAND Flash, che seleziona la pagina corretta utilizzando il set di decodificatori di blocco e pagina. Una volta che il blocco è selezionato, viene impiegato il rilevamento della corrente delle linee di bit per determinare se il floating gate in una cella NAND contiene carica o meno. Ciò si ottiene pilotando la tensione del control gate delle word line non selezionate a Vread. Questo fa sì che altre celle di memoria nella stringa servano come “transfer gate”. La tensione del control gate della word line selezionata è impostata su 0V. Se il floating gate non contiene carica, la cella di memoria è attiva (il trasferimento è di tipo a esaurimento) e la corrente scorre attraverso la stringa. Se il floating gate contiene carica, la cella di memoria non è attiva perché il floating gate ha una tensione di soglia più elevata e la corrente non scorre attraverso la stringa. I “sense amplifiers” collegati a un’estremità della linea di bit rilevano il flusso di corrente. L’assenza del flusso di corrente è considerato un “1” logico mentre la sua presenza indica uno “0”. I dati sono quindi trasferiti dai latch al controller dove la logica ECC esegue il controllo degli errori e correzione.

Fonte: "Errors in Flash-Memory-Based Solid-State Drives: Analysis, Mitigation, and Recovery"

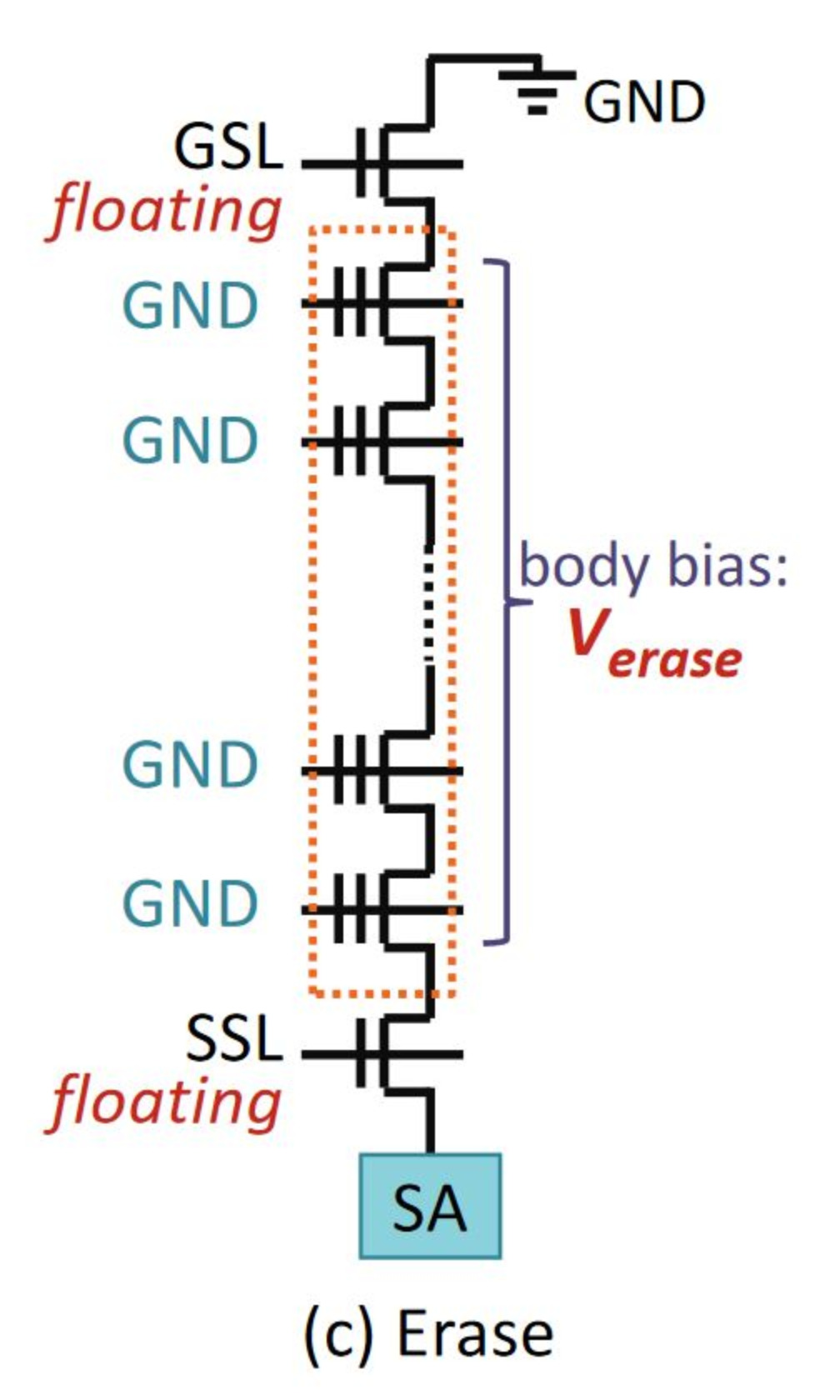

# Operazione di cancellazione

Quando l’FTL nel controller determina che il numero di pagine libere è estremamente basso, il controller invia un comando di cancellazione alle NAND Flash. I livelli dell’FTL hanno la propria politica per determinare quale blocco deve essere recuperato. Una volta che l’indirizzo fisico del blocco da cancellare è determinato dal controller, questo viene passato alla NAND Flash. La control unit nella NAND Flash seleziona il blocco da cancellare utilizzando il decodificatore di blocco. I control gate di tutte le word line nel blocco selezionato sono messe a terra e il “P-well” del blocco è polarizzato a Verase (tensione). Ciò causa il campo tunnel degli elettroni delle cariche del Floating Gate al P-well per le celle programmate 0, mentre le celle non programmate corrispondenti a “1” logico vengono sovracancellate. A differenza di un’operazione di scrittura in cui l’effetto tunnel avviene su più impulsi di programma, la cancellazione avviene in un singolo impulso di cancellazione perché la sovracancellazione non è un problema nelle memorie NAND Flash. Poiché più blocchi in un array condividono un P-well comune, è possibile che i blocchi non selezionati nello stesso array che condividono lo stesso P-well possano essere inavvertitamente cancellati. Sono state proposte diverse tecniche per inibire la cancellazione dei blocchi non selezionati. Una di queste tecniche è chiamata “inibizione della cancellazione automatica” che utilizza l’accoppiamento capacitivo tra i control gate delle varie celle e il P-well. Prima di applicare la tensione di cancellazione al P-well, i control gate dei blocchi non selezionati delle NAND Flash che condividono lo stesso P-well con il blocco selezionato vengono fatti galleggiare chiudendo i “pass gate”. I control gate sono accoppiati dato che il P-well è polarizzato su Verase, il che fa sì che i blocchi non selezionati vengano automaticamente inibiti dalla cancellazione.

Fonte: "Errors in Flash-Memory-Based Solid-State Drives: Analysis, Mitigation, and Recovery"

# Data Retention

Abbiamo detto che le NAND Flash sono delle memorie di tipo non-volatile, quindi che mantengono la carica elettrica per un determinato periodo senza essere alimentate. Sono in grado di fare ciò visto che il floating gate ha capacità conduttive ed è in generale di tipo poli-siliconico. Bene, questo tempo - quindi il tempo in cui mantengono i dati nel floating gate senza alimentazione - è definito come “data retention” e ha una determinata durata che può essere impattata da diversi fattori, partendo dalle temperature; anche un grado può far variare sensibilmente il data retention, cosa che abbiamo spiegato nell’articolo pensato per quest’ultime.

Per questo motivo dischi che hanno le NAND Flash - proprio come gli SSD (e gli SSHD, nonostante quest’ultimi siano in capacità molto più ridotta) - non sono adatti per backup “rari” (cioè che vengono fatti sporadicamente), può essere che in una settimana il nostro SSD senza corrente perda completamente i dati, ma può essere anche 8 mesi. Ogni produttore testa le NAND Flash per imporre un data retention con una determinata e costante temperatura, per esempio, le Micron B27B - che sono delle 96L TLC - sono state testate per un data retention di 6 mesi a 55 gradi. Oppure le loro (Micron) QLC 96L - modello N28A -, testate per un Data-retention di 4 mesi a 40 gradi. Ciò non significa che se il nostro SSD ha le NAND prima citate avrà quell’esatto data retention, visto che le nostre temperature delle NAND sono diverse da quelle delle aziende.

Quindi, se abbiamo un SSD come supporto per il sistema operativo e abbiamo lasciato il PC senza corrente per un po’ di tempo ma non troviamo più i dati, è normale.

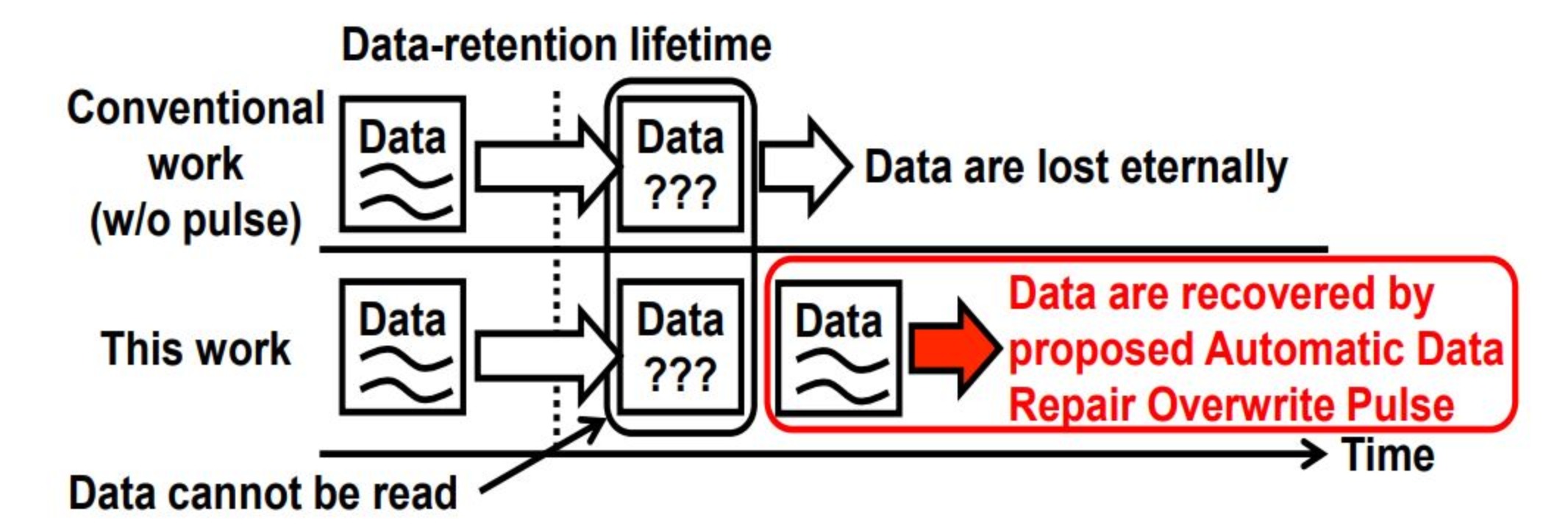

Da tempo esistono diverse tecniche per migliorare il data retention delle NAND. Purtroppo non lo si può “sconfiggere” visto che è un fenomeno che rientra nella natura delle NAND Flash (e probabilmente di tutte le memorie di tipo non-volatile). Per citarne una, nel 2019, diversi ingegneri con l’IEEE hanno presentato una tecnica che sulla carta è in grado di migliorare di 38.3 volte il data retention: l’ADROP (Automatic Data Repair Overwrite Pulse).

l’ADROP è una tecnologia che entra in gioco quando ECC non è in grado di correggere gli errori. In questo caso l’ADROP sovrascrive i dati (inclusi gli errori nelle celle di memoria) e quindi “inietta” gli elettroni nelle celle di memoria che sono stati persi durante il data retention dalla NAND. In questo modo l’ADROP è in grado di fare durare il data retention ben 38.3 volte. l’ADROP è composto dal “Vth Shift Recovery Pulse (VSRP)” e dal “Data Repair Pulse (DRP)” che sono implementati nel controller SSD senza un sovraccarico nella parte della circuiteria.

Qui una rappresentazione basilare di quello che fa l’ADROP, sopra senza e sotto con:

Fonte: "Automatic Data Repair Overwrite Pulse for 3D-TLC NAND Flash Memories with 38x Data-retention Lifetime Extension"

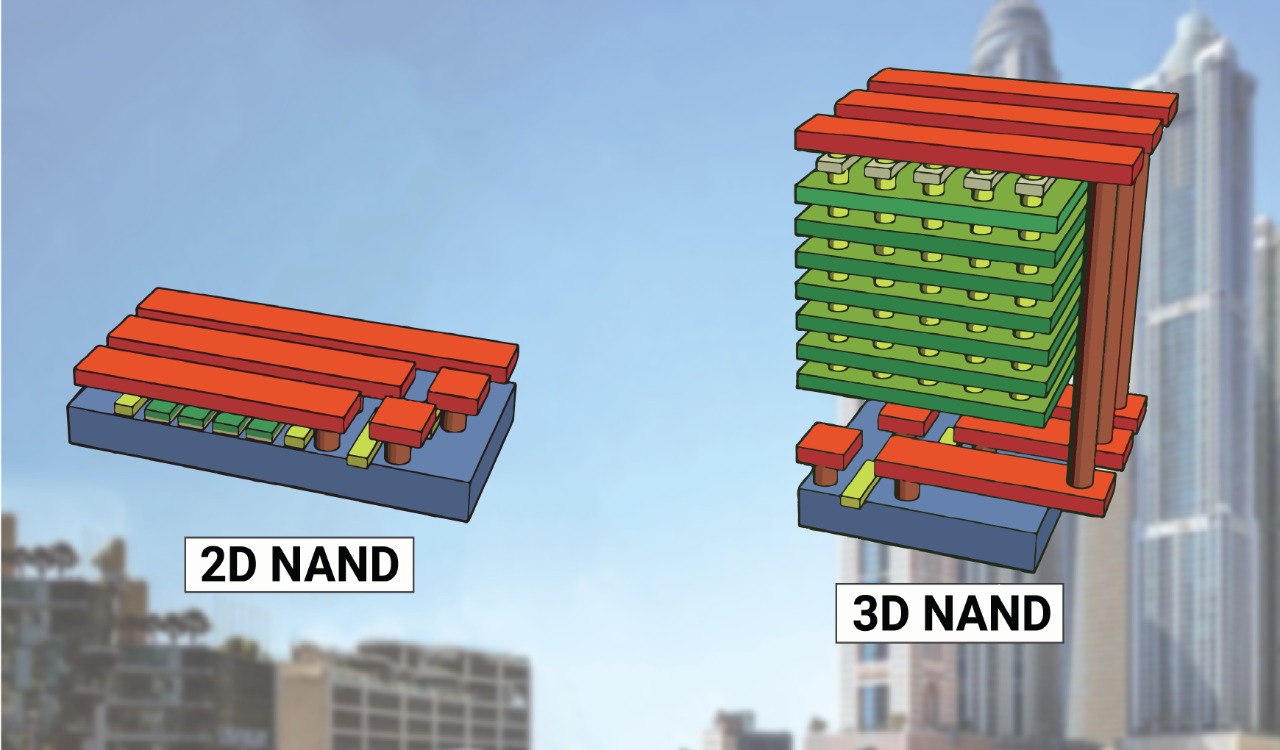

# NAND 2D VS NAND 3D

Al giorno d’oggi ci sono due principali “tipi” di NAND diffuse nei mezzi di memorizzazione dati: le 2D NAND e le 3D NAND. Quest’ultime sono ancora in produzione e più diffuse, a differenza delle le 2D NAND che sono reperibili solo in qualche SSD (per esempio le vecchie versioni dei WD Blue e alcuni Kingston A400 le sfruttavano).

La differenza principale tra 2D NAND e 3D NAND è che le 2D sono planari (orizzontali) mentre le 3D sono verticali. Ciò permette alle 3D di avere una maggiore scalabilità (anche in termini di processo produttivo), performance, affidabilità e un minor consumo energetico (allo stesso tempo maggiore efficienza). Tuttavia hanno costi di produzione più alti perché se durante la produzione si sbaglia un punto bisogna rifare tutto da capo. Le 3D NAND sono entrate in gioco principalmente per il motivo che le 2D cominciavano a perdere troppa energia con i nuovi processi produttivi e perché le 3D NAND essendo più scalabili portano a maggiori capacità. Tuttavia un processo produttivo inferiore porta anche svantaggi, infatti il processo produttivo in sé determina la grandezza di ogni cella nella NAND, quindi più è piccolo questo numero più piccole sono le celle e meno elettroni posso immagazzinare, e ciò comporta una peggiore durata.

Qui una comparazione fisica tra 2D e 3D NAND:

Fonte: NVMdurance

# X-NAND

Durante il “three-day virtual” di Flash Memory Summit (FMS) nel 2020, Andy Hsu, il CEO e fondatore di NEO Semiconductor, ha portato una dettagliata presentazione che riguarda l’architettura X-NAND flash e che promette di combinare la velocità delle NAND di tipo SLC con una densità e un basso prezzo simile a quello delle NAND di tipo QLC. L’azienda ha mostrato per la prima volta le loro X-NAND nel 2018 come soluzione di archiviazione per i mercati emergenti di intelligenza artificiale e 5G, arrivando al three-day virtual spiegandone tutti i dettagli.

Come abbiamo già spiegato in questo articolo, le QLC hanno un costo del die inferiore rispetto alle TLC e una maggiore densità (fattore utile per produrre SSD con maggiori capacità), ma allo stesso tempo, come svantaggi, hanno una durata e prestazioni sensibilmente peggiori. Verso il 2025/2026 gli analisti prevedono l’esordio delle celle PLC (Penta Level Cell) e OLC (Octa Level Cell) con l’utilizzo di diverse tecnologie, quindi ci sposteremo verso in “peggio”, e le X-NAND servono per colmare questi problemi avendo un prezzo accettabile.

Come possiamo ben vedere nella figura qui sotto le X-NAND sono in grado di aumentare le performance rispetto alle NAND QLC “normali” di davvero molto: si afferma che le X-NAND possono eseguire carichi di lavoro di lettura e scrittura casuali 3 volte più veloci rispetto alle NAND Flash di tipo QLC e di essere più veloce di 27 e 14 volte per carichi di lavoro di lettura e scrittura sequenziali rispettivamente. Per avere queste prestazioni le X-NAND implementano nel die 16 piani con una dimensione del 37% più piccola rispetto a un die da 16 piani di una normale NAND Flash e delle pagine molto più piccole, ovvero da 1 KB (contro 16 KB)

Fonte: Tom's Hardware

Qui una rappresentazione a destra del die da 16 piani delle X-NAND e del die da 16 piani di una NAND Flash:

Fonte: Tom's Hardware

Come possiamo ben vedere, anche durante la scrittura sequenziale il comportamento delle X-NAND è eccellente: nonostante le QLC “cadano” di velocità dopo la saturazione della cache SLC, le X-NAND mantengono pari performance per tutto il tempo, come lo fanno le NAND SLC:

Fonte: Tom's Hardware

Nella speranza che queste memorie arrivino nella fascia consumer degli SSD, questa tecnologia mira a ambiti di dispositivi embedded, intelligenza artificiale e cloud, includendo NAS, data center ed edge computing.

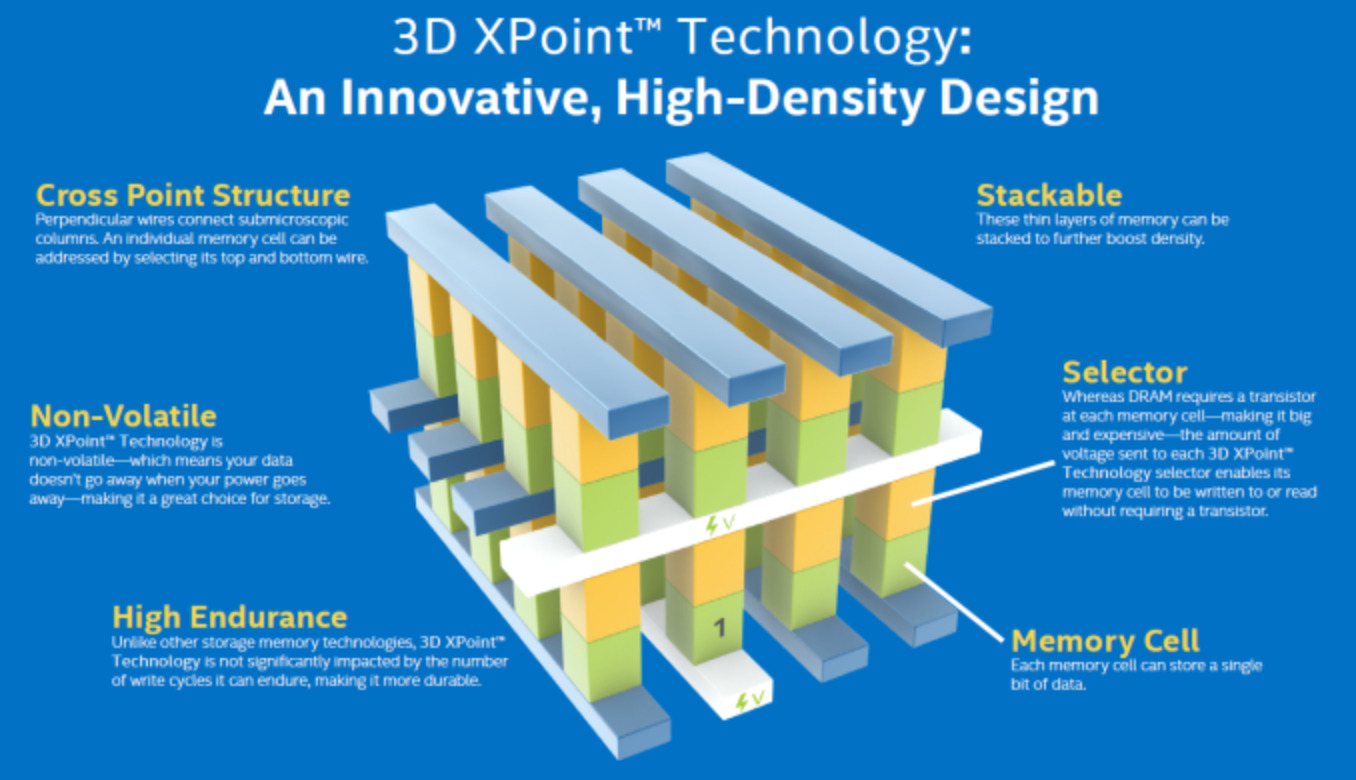

# PCM (3D XPoint)

Un altro tipo di memoria non-volatile sono le Intel 3D Xpoint (o “Optane”) che sono completamente diverse dalle NAND classiche negli SSD per come archiviano i dati e per come sono fatte (sono una lega di metalloidi e non usano il silicio) e che ha il vantaggio di essere una memoria write-in-place, ovvero riesce a evitare di eseguire i cicli P/E delle NAND in modo tale da avere una resistenza infinitamente più lunga. Ciò rende questo tipo di memoria meno dipendente dall’over-provisioning e dalla garbage collection risultando in performance (e appunto durata) nettamente maggiori. Le PCM ermettono prestazioni eccellenti a basse profondità di coda con tempi di accesso (latenza) molto bassi. Sono valutate come memorie storage class memory (SCM) ed è un concorrente di altre memorie NAND SLC come le Z-NAND di Samsung e le XL-FLASH di Kioxia. Queste NAND sono disponibili negli SSD Optane di Intel che purtroppo sono usciti dalla fascia consumer da diverso tempo. Un esempio è l’Intel Optane SSD DC P5800X che è pensato per utilizzo data center e che possiede le 3D XPoint di seconda generazione.

Fonte: AnandTech

# DRAM Cache

# Come funziona la DRAM Cache?

La DRAM cache è un tipo di memoria voltatile (che troviamo anche nella memoria RAM) ed è un altro componente che può esserci negli SSD, in qualsiasi form factor esistente (sia 2.5’’ che sia M.2). “Può esserci” per il fatto che più che essere un componente che riunisca l’intero SSD (come lo fanno le NAND Flash e il controller) è un componente “premium” che può mancare negli SSD, ma la sua assenza comporta degli svantaggi. Per esempio, un SSD senza DRAM cache (chiamati anche “DRAM-less”) ha delle prestazioni peggiori e una durata della vita minore. Si riduce anche la scrittura sostenuta (dopo la cache SLC) e l’SSD performan peggio, anche per quel che riguarda la scrittura random (ovvero file da 4 KB nel nostro sistema operativo o programmi), mentre ha una durata della vita inferiore perché con una DRAM cache l’SSD ha un write amplification factor (WAF) minore.

# Perché un SSD con la DRAM cache va meglio in W/R random 4K?

Perché i dati di mappatura richiedono 1 byte di mappatura per 1 kilobyte di dati, traducendo l’indirizzamento a 32 bit (4 byte) per ogni 4 KB di dati. 4 KB tende ad essere la dimensione standard del cluster del sistema operativo e inoltre, le dimensioni del settore sono fisicamente 4 KB - 4Kn o “Advanced Format (“Formato Avanzato”)”. Con 512e c’è più sovraccarico di metadati e i blocchi logici da 512 byte sono mappati a un blocco fisico da 4096 byte a livello di file system. Questo sovraccarico è possibile ridurlo tramite compressione di dati, per esempio indirizzando un punto di partenza/offset con un numero di unità di dati contigue come un blocco più grande, ma comunque è tipico per un SSD da 1 TB avere 1 GB di DRAM. Avere meno di questa quantità ottimale di DRAM può influire sulle prestazioni dell’unità in determinate circostanze. Questo perché la mappatura può essere FGM (fine-grained) o CGM (coarse-grained) con vari compromessi a causa delle dimensioni della pagina fisica che diventano più grandi di 4 KB (per esempio 16 KB con le attuali TLC) e richiedono quindi la gestione di sottopagine. Allo stesso modo, la mappatura a livello di superpagina potrebbe essere più grossa utilizzando blocchi più grandi.

# Un fraintendimento comune sull’utilizzo della DRAM cache

Contrariamente al pensiero comune, la DRAM cache non viene utilizzata come cache di scrittura come negli hard disk (al giorno d’oggi non è più così), ma viene usata per archiviare i metadati, inclusi dati di mappatura tra posizioni di dati fisici (PBA) e virtuali (logici o LBA), dati di livellamento dell’usura per TRIM e garbage collection (GC). Ovvero dati che contengono altri dati.

La DRAM Cache anche memorizzare pagine temporaneamente, ad esempio quelli a cui si accede di frequente durante la programmazione di buffer LSB/MSB. L’FTL viene gestito dalla DRAM cache, archiviandolo là dentro in due parti: l’allocatore che si occupa dell’indirizzamento e un “separate collector” (“raccoglitore separato” in italiano) che si occupa del Garbage Collection a livello di blocco.

Attualmente sono diversi i produttori di DRAM che troviamo negli SSD:

- Samsung

- Micron/SpecTek

- SK Hynix

- Kingston

- Nanya

- Raramente (perché destinata al mercato asiatico) UniIC.

Tutti questi produttori vendono le loro DRAM a qualsiasi tipo di azienda che produce SSD e le producono in diverse generazioni, proprio come con le RAM: DDR, DDR2, DDR3 e DDR4. Più la generazione è alta e più la DRAM sarà veloce (meno latenza) ed efficiente (meno consumo). Più è grande la DRAM e più sarà “duratura” perché sarà in grado di archiviare più metadata. La DRAM può essere in uno o più chip, solitamente con un massimo di due (per esempio nei Kingston KC2000 e KC2500). Inoltre, può essere su entrambe le facce del PCB.

# SRAM VS DRAM

Bisogna dire qual è la differenza tra SRAM e DRAM poiché c’è molto fraintendimento e confusione su questo punto, pensando che gli SSD con il controller Phison S11 (controller SATA) in ogni caso - anche con la mancanza fisica di un chip DRAM - abbiano la DRAM cache perché il controller contiene 32 MB di SRAM integrati.

Tutti i controller degli SSD (come tutte le CPU e tutti i microprocessori) hanno una certa quantità di SRAM (“statica” in quanto non ha bisogno di essere aggiornata come la DRAM/SDRAM) incorporata al loro interno. Questa memoria è più veloce della DRAM ma anche più costosa, infatti tutti i controller ne hanno poca, rispettivamente 32 MB, al massimo dei quali 4 MB sono in genere utilizzati per la mappatura (intesa come la gestione dell’FTL). Alcune “porzioni” della SRAM possono essere utilizzate per archiviare i metadati. In ogni caso, se un SSD non ha una DRAM cache esterna è considerato DRAM-less, nonostante il controller abbia 32 MB di SRAM all’interno.

Prendendo come esempio l’architettura dell’SM2262EN che abbiamo mostrato prima, possiamo notare che la SRAM si trova proprio all’interno del controller, tra i due core e la ROM:

Fonte: Silicon Motion

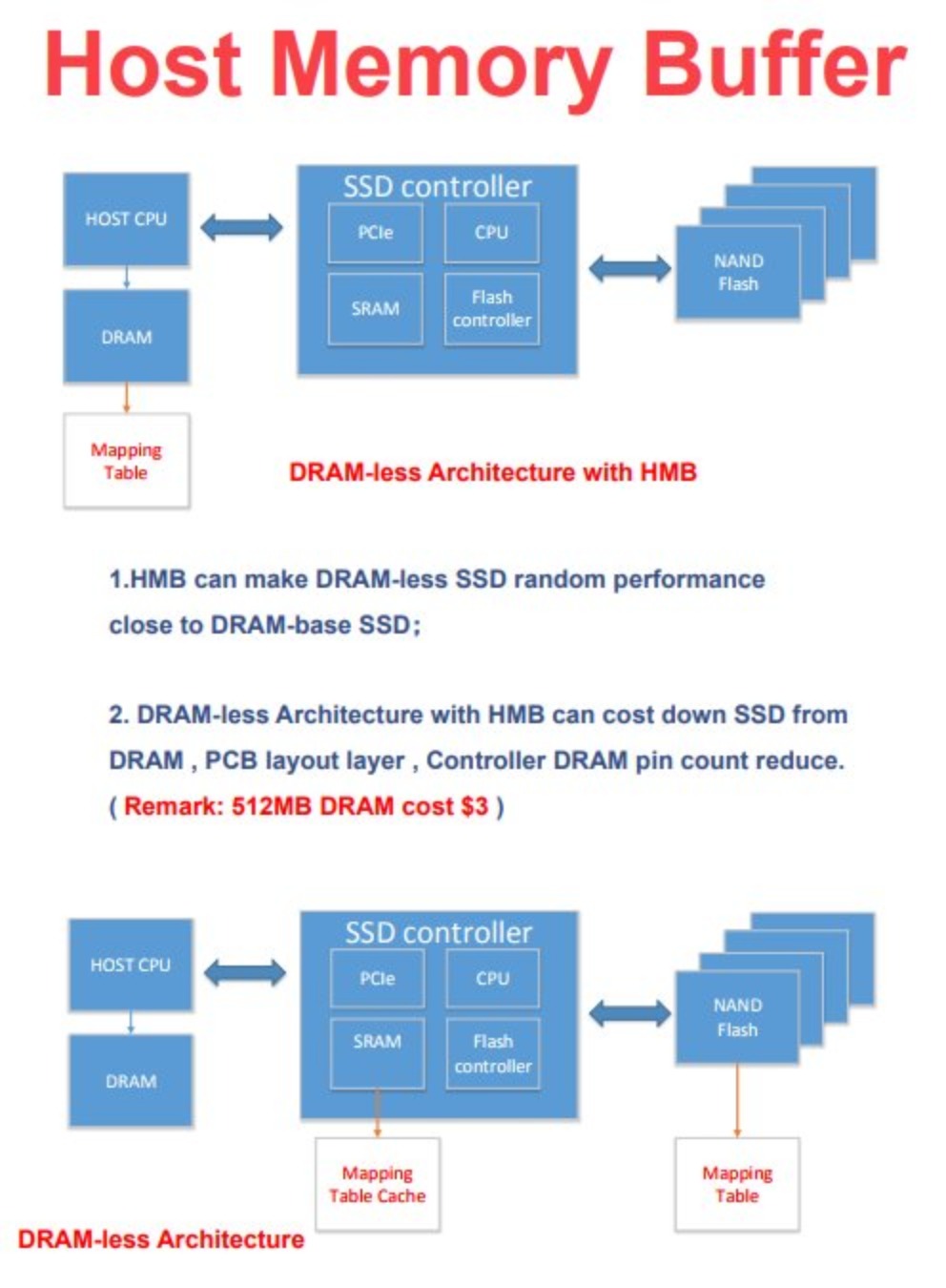

# HMB (Host Memory Buffer)

Gli SSD DRAM-less non sono così rari da trovare, sia per i SATA che per gli NVMe. Visto che gli SSD NVMe lavorano su un altro tipo di protocollo (e interfaccia), son riusciti a creare una tecnologia di nome “Host Memory Buffer (HMB)” che entra in soccorso con appunto gli SSD M.2 NVMe per aumentare le performance e la durata.

Questa tecnologia esiste da un po’ di tempo e permette al controller dell’SSD di “appoggiarsi” alla RAM utilizzandone dai 24 ai 128 MB, anche se solitamente ne utilizza sui 64 MB. L’HMB gestisce anche l’FTL. Questa tecnologia non permette di rendere l’SSD performante come se avesse la DRAM cache fisica, ma è in grado di migliorare le prestazioni, soprattutto quelle di I/O. Ovviamente dev’essere supportata dal controller per farla funzionare, non è sempre così ma gli SSD più recenti la supportano, per esempio tutti quelli con il Silicon Motion SM2263XT come controller.

Qui una foto che compara un SSD con e senza HMB; sopra HMB e sotto non:

Fonte: Courtesy of Longsys

# SLC cache

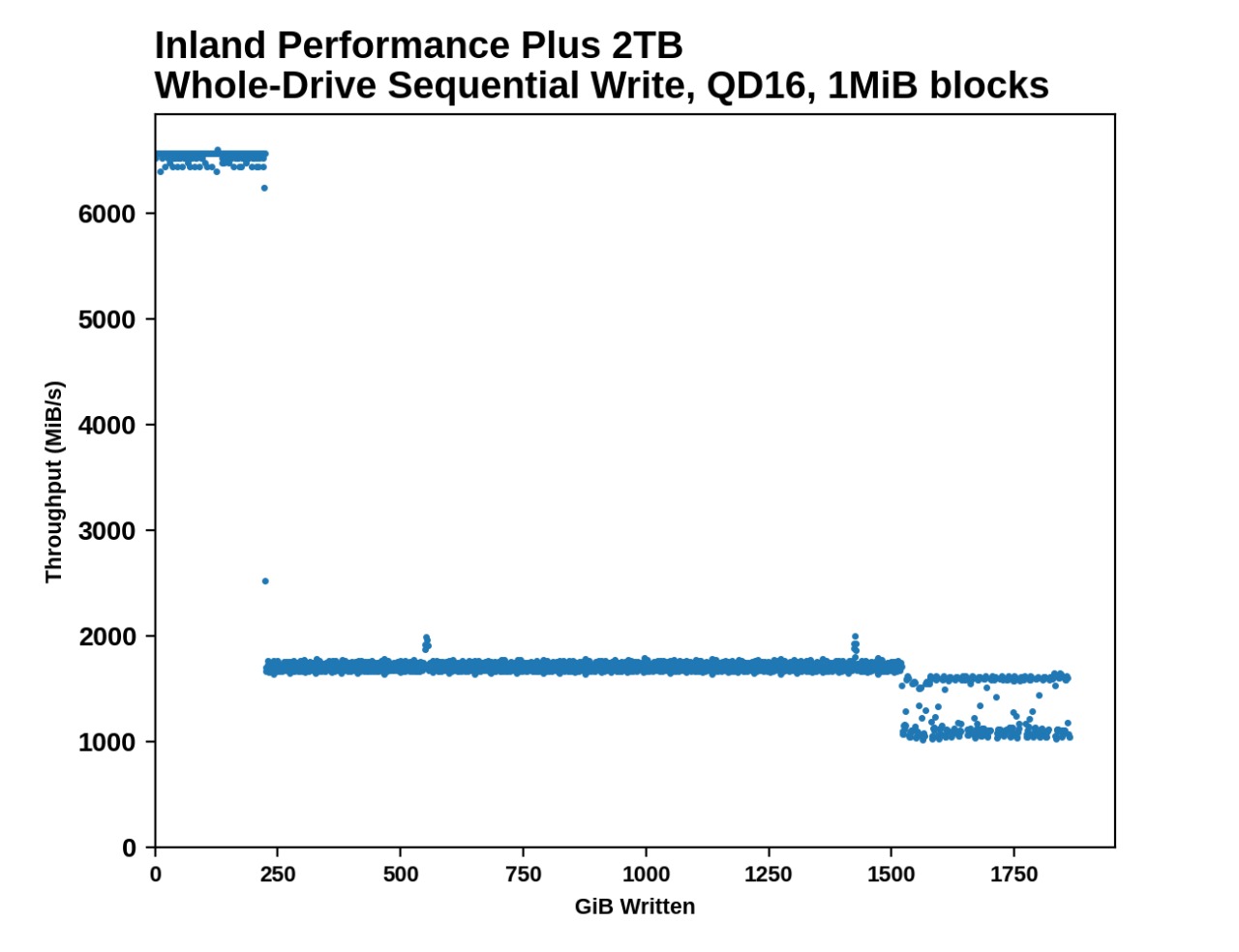

La SLC cache è una tecnologia presente ormai in tutti gli SSD che serve per aumentare le performance dell’SSD in scrittura sequenziale e la longevità del disco, se di un determinato tipo. La SLC cache non è una vera e propria NAND SLC ma è semplicemente una cache che permette di scrivere una cella per un bit (anche se è TLC o QLC), infatti può essere chiamata anche “pSLC (pseudo-SLC)”. In questo modo l’SSD prima di scrivere sulle celle (SLC, MLC, TLC, QLC) può scrivere in questa porzione di cache per avere prestazioni maggiori (dato che programma solo un bit come nelle NAND SLC) e, nel caso fosse statica, una maggiora durata. Qui un esempio con un Inland Performance Plus da 2 TB:

Fonte: AnandTech

Quindi la SLC cache ha una certa capienza (in questo caso poco meno di 250 GB) e una certa velocità (in questo caso più di 6000 MB/s), ed è per questo che sapere la scrittura sequenziale dell’SSD è molto importante, perché questa sarebbe la simulazione di un trasferimento di dati (in questo caso con una dimensione del blocco da 1 MB e una QD di 16). Ci sono casi in cui le performance non calano nonostante sia stata “superata” la cache SLC (vedere gli SSD 3D XPoint, Z-NAND, XL-Flash, gli SSD in modalità pSLC, ecc.), ma sono abbastanza rari nei TLC al giorno d’oggi.

I meccanismi della cache SLC possono essere complicati visto l’uso di algoritmi di controllo complessi, più tipi di SLC e/o zone, più stadi di prestazioni (per esempio “direct-to-NAND”), ecc. Alcune NAND Flash possono avere aree separate e che possono essere in diversi stati contemporaneamente, tra cui quelle con i blocchi ibridi. Per esempio le Kioxia BiCS4 QLC da 96L (attualmente molto poco diffuse), possono funzionare in modalità pSLC, in modalità pTLC (pseudo-TLC) e QLC “puro”. Un altro aspetto del comportamento SLC è la strategia dell’allocazione delle pagine. Ad esempio, la tecnologia “TurboWrite” di Samsung allocherà l’SLC per le scritture dell’utente finché l’SLC è disponibile. Più precisamente, la tecnologia TurboWrie permette di avere sia una cache SLC dinamica che una cache SLC statica e non solo gli SSD Samsung adottano questa tecnologia: anche Sabrent e WD hanno iniziato. WD fin dai loro PCIe 3.0 NVMe (come il WD SN750) con il nome di “nCache” e Sabrent con il Rocket 4 Plus, un PCIe 4.0. C’è anche l’utilizzo della migrazione dei dati, ovvero che il controller in uno stato di idle (ovvero in uno stato in cui non esegue nessuna operazione) migra i dati dall’SLC al TLC.

# Statica

La cache SLC di tipo statico è sempre disponibile e rimane in modalità SLC per sempre dato che si trova nell’over-provisioning (OP) dichiarato, uno spazio riservato nell’SSD al quale l’utente non può accederci. Poiché questo tipo di cache SLC è riservato ed è sempre disponibile fino alla fine della vita dell’SSD, ha una resistenza molto più elevata rispetto alle NAND Flash di base. La cache SLC di tipo statico può consentire un “write amplification factor (WAF)” a 1.0 da che quest’ultimo si applica solo alla NAND Flash nativa (TLC, QLC, ecc.) e molte scritture possono essere rinviate, con la consapevolezza che la modalità pSLC ha una resistenza P/E molto più elevata.

# Dinamica

Un altro tipo di cache SLC è quello dinamica: varia in disponibilità a seconda dello spazio utilizzato dall’utente, diminuendo di dimensioni man mano che l’SSD viene riempita (e non usato). La cache SLC tende a essere molto meno performante rispetto alla cache SLC statica visto che prevedere i futuri carichi di lavoro che verrano svolti sulla cache ed eseguendo un’ottimizzazione durante lo svuotamente di quest’ultima (ovvero in uno stato di idle), in modo tale da bilanciare la grandezza della cache stessa con le operazioni future. Questo processo solitamente aumenta il write amplification factor diminuendo la vita delle NAND (e quindi anche quella dell’intero SSD). La cache SLC dinamica, a differenza di quello statica, condivide una “zona di usura” con la NAND Flash nativa (per esempio TLC) influenzando il garbage collection e aumentando il sovraccarico sul controller.

# Ibrida

Esiste un design della cache SLC che è sia statico che dinamico: l’ibrido. Non è presente in tutti gli SSD dato che è una tecnologia abbastanza complicata da implementare e da far utilizzare al controller, ma offre un maggiore bilancio. Samsung questo design lo chiama come “TurboWrite”, WD come “nChache”, ma lo utilizza anche Sabrent, a quanto pare anche Crucial (solo sul P5) e altre aziende. Per ridurre il numero di cancellazioni con questo tipo di cache il controller può usare uno schema a blocchi ibridi, ovvero che in alcuni momenti alcuni blocchi vengono programmati in un solo bit (SLC) mentre in altri momenti altri blocchi vengono programmati nel numero di bit della NAND, ovvero TLC, QLC, ecc.

# Funzioni e software per SSD

# Sistemi per RAM Cache (Momentum Cache, Rapid Mode)

Alcuni produttori per certi SSD hanno dei “sistemi” (attivabili tramite il loro software) che permettono di utilizzare parte della RAM del proprio PC (circa il 25%) come cache all’SSD per aumentare esponenzialmente le prestazioni in scrittura e lettura sequenziale; i sistemi più comuni sono la Momentum Cache di Crucial e la RAPID Mode di Samsung.

La Momentum Cache di Crucial funziona sui SATA più recenti di casa loro e teoricamente su ogni SSD NVMe mentre la RAPID Mode di Samsung funziona sui loro SSD più recenti (dalla serie 840 in su) ed è attivabile tramite il loro software Samsung Magician dalla versione 4.2 in su.

Tuttavia non consigliamo di attivare sistemi come questi dato che - oltre a prendere massimo il 25% della RAM (infatti è consigliata in presenza di più di 8 GB di RAM, con un tetto massimo massimo di 4 GB in uso) - sistemi moderni come Windows 10 sono già in grado di fare caching e ci sarebbero solo un sovraccarico. Oltretutto all’atto pratico, nonostante le performance aumentino di molto nei benchmark, la differenza è davvero poca.

# S.M.A.R.T.(Self-Monitoring, Analysis and Reporting Technology)

Lo S.M.A.R.T. (Self-Monitoring, Analysis and Reporting Technology) è un sistema di monitoraggio della salute di un disco SSD, HDD o eMMC. La sua funzione primaria è quindi quella di rilevare gli errori che possono peggiorare l’affidabilità del disco e quindi è utile per prevedere la morta del disco. Lo S.M.A.R.T., come già detto in precedenza, è una delle tante funzioni che viene gestita nell’FTL da parte del controller.

È possibile monitorare lo S.M.A.R.T. tramite software come CrystalDiskInfo o Hard Disk Sentinel, ma anche i software proprietari delle aziende degli SSD (nel caso ci fosse) vanno bene.

Tutti i parametri sono da considerare, ma non limitiamoci a vedere solo la percentuale e i colori dei pallini affianco i parametri ma anche i valori grezzi (che di predefinito sono in esadecimale e non decimale, quindi da convertire).

# Secure Erase

Il secure erase è un comando ATA che viene eseguito a basso livello e che permette di far inviare dei comandi dal firmware al controller dell’SSD per impostare tutte le celle flash nelle NAND come “vuote”, riportandole allo stato di fabbrica. Diciamo che può essere vista come una formattazione, ma molto più aggressiva rispetto a quella “normale”.

Il secure erase cancella i dati di “mappatura” dell’unità mentre il suo "disinfettante (dall’inglese “sanitize”) allo stesso tempo lo fa e cancella inoltre i blocchi. Per una corretta pulizia di un’unità è meglio eseguire una disinfezione (sanitize) o un secure erase seguito dall’inattività dell’unità.

È consigliato di effettuare un secure erase in casi di “emergenza” (solo quando necessario, magari nel sospetto della presenza di un bug) e non per casi “banali”. Per effettuare un secure erase si può utilizzare il software che l’azienda prodruttice dell’SSD offre, sempre nel caso ci fosse. Nel caso l’azienda non offrisse alcun software per effettuare un secure erase si può utilizzare quello del BIOS della scheda madre.

Naturalmente, dopo un secure erase è impossibile recuperare i dati cancellati, proprio perché le celle vengono completamente ripristinate e vengono fatte tornare al loro stato di fabbrica.

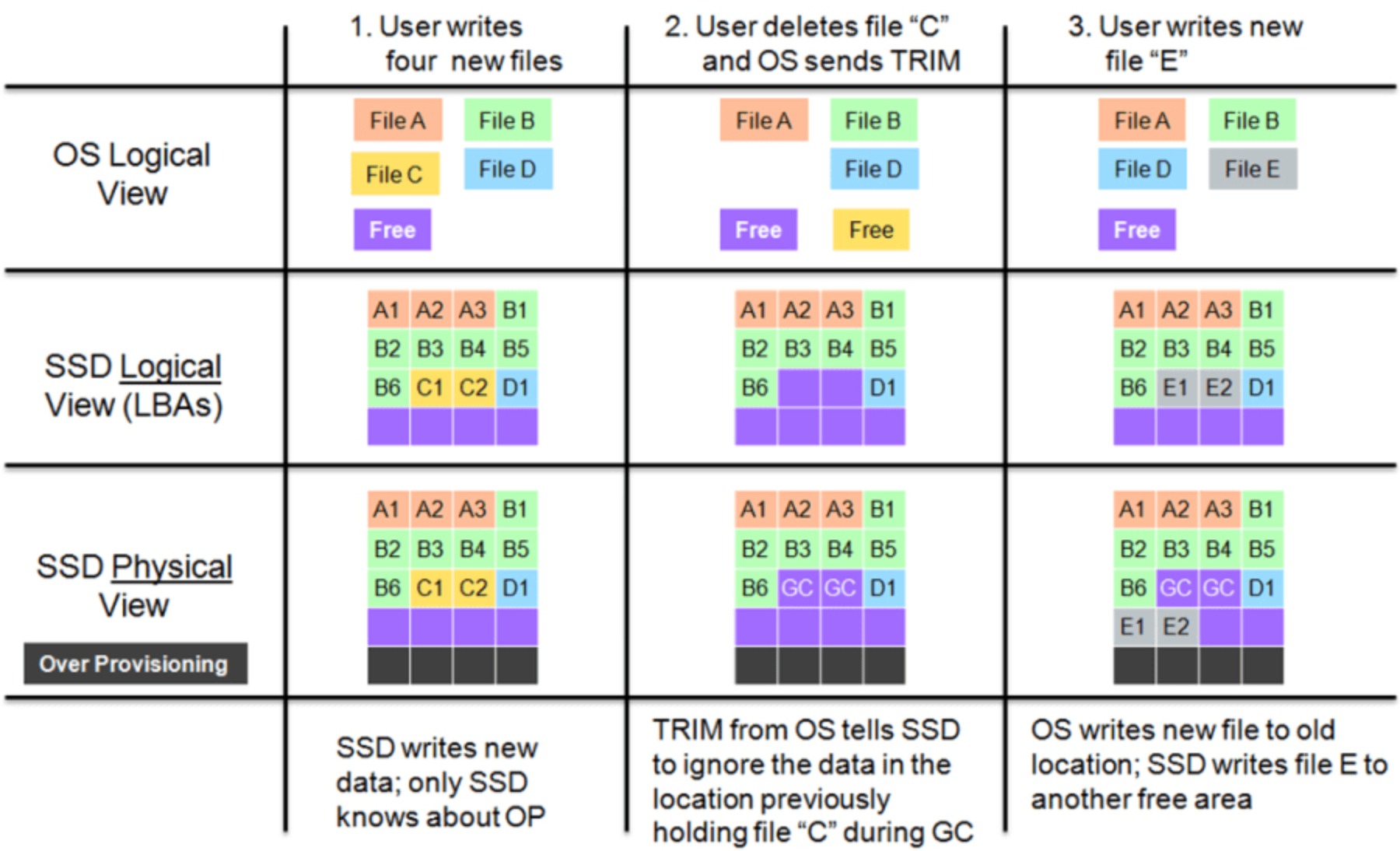

# Garbage Collection e TRIM

Come già abbiamo spiegato in precedenza, le NAND Flash sono organizzate in blocchi composti da una serie di pagine. I dati possono essere scritti sulle pagine in qualsiasi momento se questa non risulta scritta o cancellata. Tuttavia, la memoria flash non può cancellare singole pagine all’interno di un blocco; l’intero blocco deve essere cancellato per riscrivere nuovamente le pagine. Per liberare le vecchie pagine e preservare le pagine aggiornate, le pagine correnti vengono prima copiate in un altro blocco disponibile, mentre le pagine vecchie o non necessarie vengono scartate. Quindi il blocco appena scritto finisce per contenere solo le pagine correnti e il blocco precedente può essere cancellato e liberato per il riutilizzo. Ecco, questo è il compito del garbage collection (GC): cancellare/liberare i blocchi e scartare le pagine vecchie.

Il TRIM invece è un comando AT che contrassegna i blocchi come inutilizzati per il sistema operativo, quindi è considerabile come l’aiutante del garbage collection. Un sistema operativo (come Windows) ottimizza un SSD eseguendo il retrim, quindi contrassegnando i blocchi “finiti” e che verranno cancellati per delle scritture future. Visto che le NAND per essere riscritte devono essere cancellate, il TRIM assieme al garbage collection è un comando importante per mantenere al meglio la salute e le prestazioni dell’SSD. Punto da tener conto è che il TRIM è meno importante sulle unità più moderne dato che il garbage collection è più aggressivo, specialmente con la memorizzazione dei bit nella cache SLC. Dopo che il TRIM ha svolto il suo compito, ci sono diversi modi in cui i valori verranno letti: non deterministico (ogni lettura restituirà dati diversi), deterministico (DRAT - tutti i dati restituiranno lo stesso) e deterministico di lettura zero (RZAT - tutti i comandi restituiscono zero).

Il recupero dei dati dopo il TRIM è qualcosa di fin troppo difficile da eseguire, quasi impossibile, per questo quando accidentalmente viene cancellato un file sull’SSD e lo si vuole recuperare bisogna portarlo a un’azienda che fa questo mestiere. Il TRIM (con il garbage collection) è presente anche negli HDD SMR.

Qui una rappresentazione del garbage collection con il TRIM:

Fonte: The SSD Review

# Wear leveling

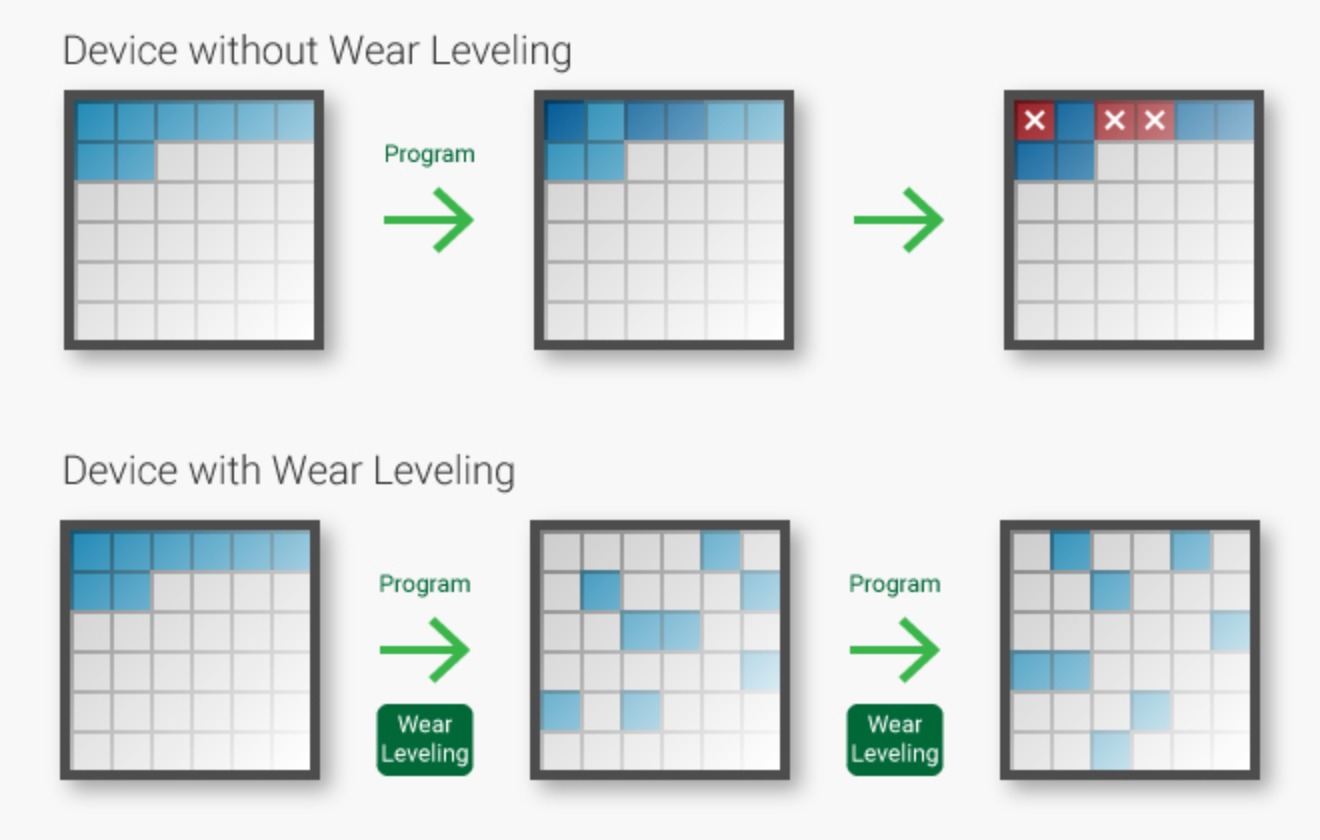

Dato che gli SSD, a differenza degli hard disk, hanno una vita delle NAND Flash definita in cicli P/E, il wear leveling serve per assicurarsi che tutta la NAND Flash dell’unità sia usurata in modo uniforme per mantenere le prestazioni e la resistenza generale anticipando quali pagine verranno scritte successivamente. Senza il wear leveling ci sarebbe il rischio che alcune aree o blocchi delle NAND Flash si usurebbero prima rispetto ad altre aree o blocchi nonostante gli SSD abbiano dei blocchi di riserva (limitati). Il wear leveling fa parte dei metadati tracciati dell’FTL.

Il wear leveling può essere suddiviso in due tipi principali: il tipo statico, che sposterà i dati statici dai blocchi in base al conteggio delle cancellazioni e il tipo dinamico, che utilizza il successivo blocco libero in base al conteggio delle cancellazioni.

Qui una rappresentazione del wear leveling; sopra senza e sotto con:

Fonte: Transcend

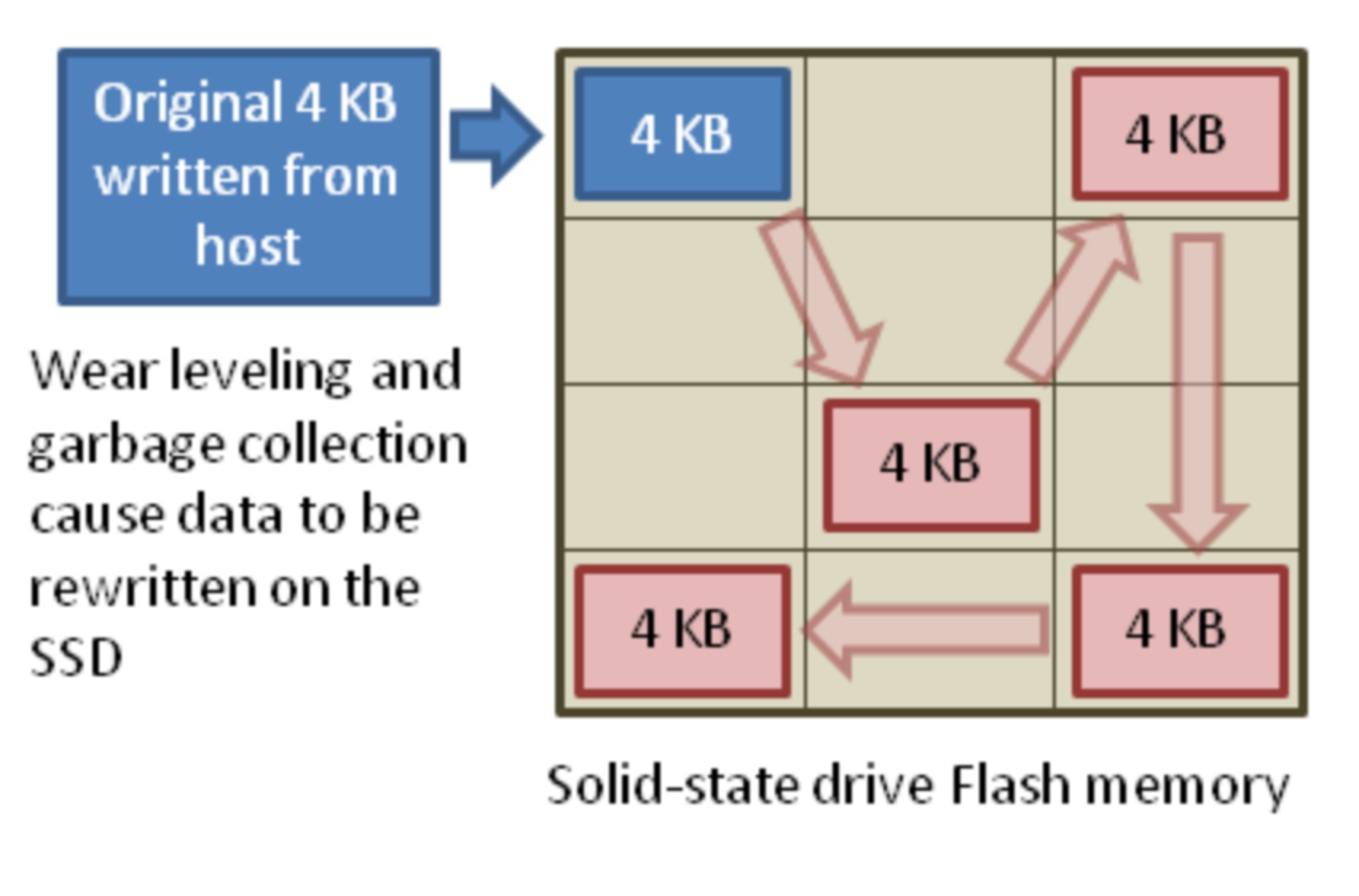

# Write amplification factor (WAF)

Il write amplification factor (WAF) è un fenomeno di ogni SSD che si verifica quando la quantità effettiva di dati fisici scritti è maggiore della quantità di dati logici scritti dal computer host, più precisamente è solitamente il doppio. Ci sono due fattori principali che causano questa differenza: il primo fattore è che ogni dispositivo di archiviazione che utilizza la memoria NAND Flash è costituito da blocchi che devono essere cancellati prima di poter essere riscritti, e il secondo fattore è che le NAND Flash possono essere scritte una singola pagina alla volta (a eccezzione delle X-NAND) e allo stesso tempo possono essere cancellati solo un blocco alla volta, e un blocco può contenere centinaia di pagine. Ciò richiede lo spostamento interno dei dati utente salvati in operazioni in background per liberare pagine adiacenti di dati che possono essere cancellate e quindi che possono essere rese disponibili per nuovi dati scritti dal computer. La conseguenza è che il numero totale di scritture effettive su un SSD è superiore al numero di scritture previste per essere scritte dal computer. Il WAF è la rappresentazione matematica di questo fenomeno.

Il write amplification factor di un SSD può essere calcolato tramite il rapporto tra le scritture fatte sulle NAND e quelle fatte dall’host (OS); chiaramente, più è grande il numero e peggio è. La “quantità” ideale di WAF è 1.0 in modo da massimizzare la vita dell’SSD.

Qui una rappresentazione del WAF; il wear leveling e il garbage collection contribuiscono nell’aumentare il WAF generale:

Fonte: Wikipedia

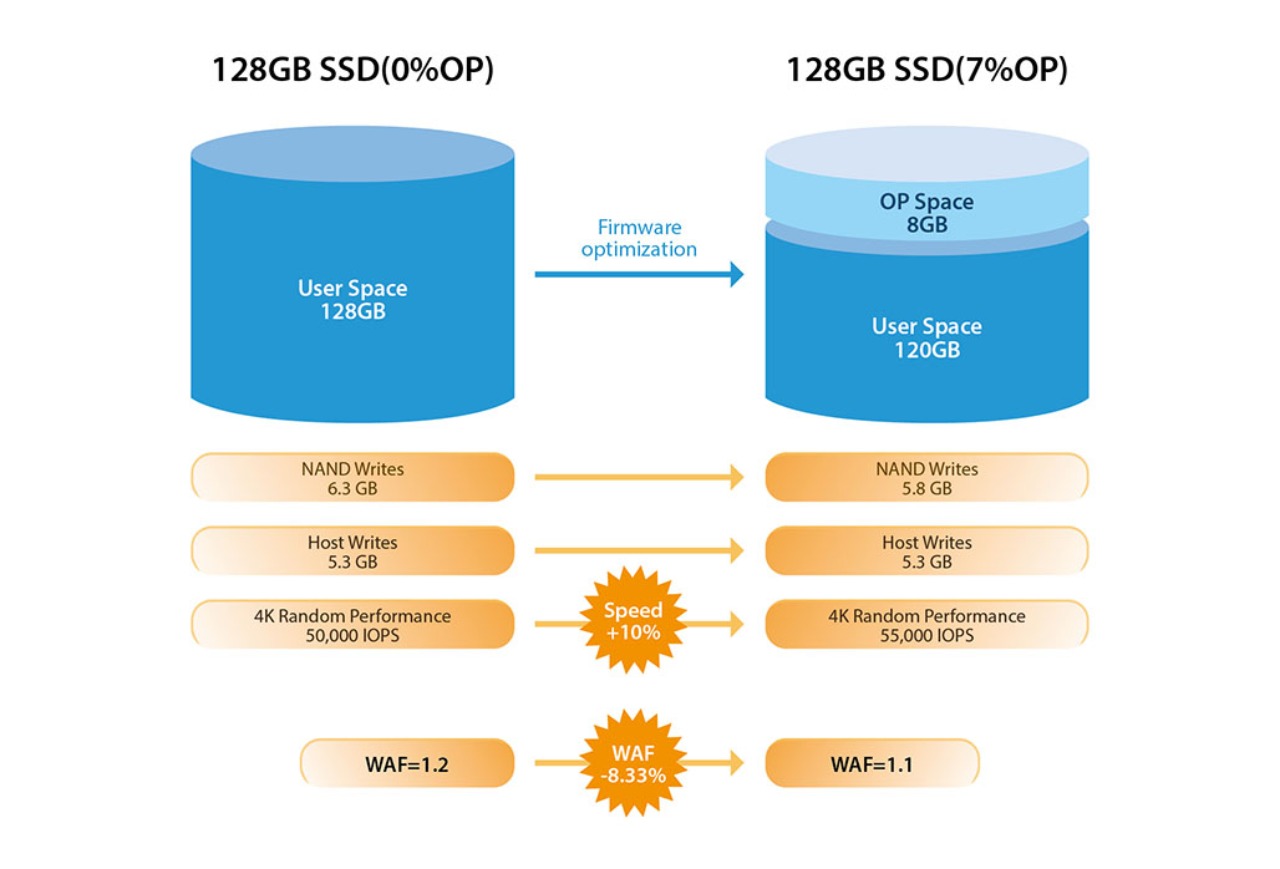

# Over-provisioning (OP)

Abbiamo già parlato di che cosa sia l’over-provisioning in un articolo, ma in questo caso entreremo un po’ di più nel dettaglio. L’over-provisioning è una “tecnologia” che riserva alcuni flash che sono garantiti per eseguire scritture (blocchi cancellati). Per via la natura delle NAND Flash, un maggiore over-provisioning può portare diversi vantaggi come: maggiori prestazioni di scrittura, resistenza maggiore dell’unità, migliore gestione del wear leveling e una possibile diminuzione del WAF, anche se un maggiore over-provisioning causa una capacità di archiviazione all’utente minore. All’interno dell’OP sono riservati anche blocchi di flash di cui abbiamo già parlato prima e di cui hanno un numero limitato (infatti nel caso si dovessero terminare - cosa vedibile tramite lo S.M.A.R.T. sull’attributo 180 - l’SSD entrerebbe in modalità di sola lettura e non sarebbe più utilizzabile come disco “normale”). Alcuni SSD possono modificare dinamicamente la quantità dell’OP durante la durata delle NAND flash per bilanciare prestazioni e resistenza e possono utilizzare qualsiasi spazio libero come OP dinamico dovuta dalla natura “aggressiva” del garbage collection e del TRIM (per questo è sempre meglio lasciare un po’ di spazio libero nell’SSD senza riempirlo completamente, così facendo si avrebbe un funzionamento generale dell’SSD migliore e una minore usura). Solitamente viene allocato un 7% di OP negli SSD più recenti e tramite gestione dischi è aumentabile. Per esempio, se un SSD da 2 TB ha 48 GB di OP, l’utente non potrà utilizzare quei 48 GB (in questo caso un SSD da 2 TB - 2000 GB - nonostante l’OP da 48 GB risulterebbe da 1863 GB per diversi motivi che abbiamo spiegato qui).

Qui una foto che mette in mostra a sinistra un SSD da 128 GB senza OP e a destra uno con il 7% sempre da 128 GB:

Fonte: Transcend