AMD Strix Point: nuovi dettagli su Zen 5 e Zen 5c

26 luglio 2024

1721977740000

Durante una sessione di Q&A e con la stampa sulla sua architettura, Mike Clark, capo dell'architettura dei core CPU "Zen", ha dichiarato: " Zen 5c utilizzato in Strix ha un percorso dati di 256-bit, così come Zen 5 presente in Strix", aggiungendo che: "Quindi non c'è alcuna differenza nella larghezza di banda vettoriale quando si passa da un core Zen 5 a un core Zen 5c".

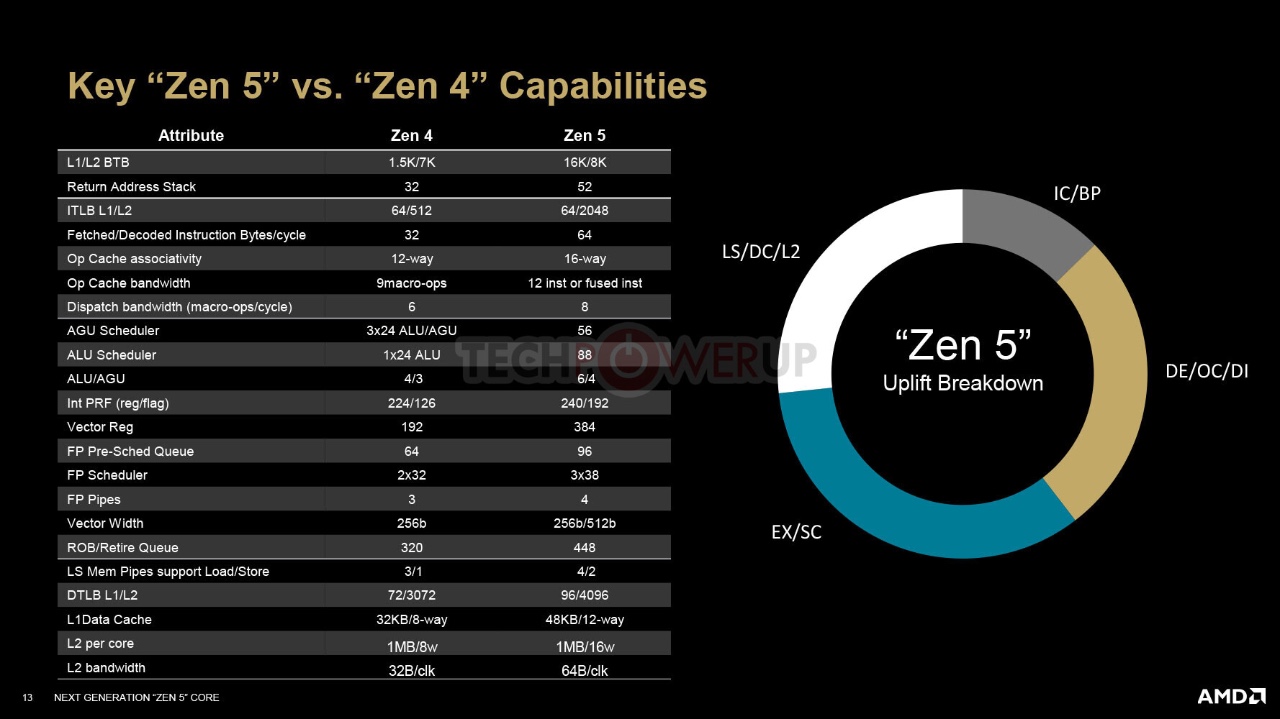

La microarchitettura “Zen 5” è caratterizzata dalla sua unità a virgola mobile che supporta AVX512 con un percorso dati completo di 512-bit, mentre nella generazione precedente “Zen 4”, AVX512 veniva gestito utilizzando una FPU da 256-bit con doppia pompata.

Non è chiaro come l’assenza di un percorso dati FP a 512-bit influenzi le prestazioni delle istruzioni rilevanti per l’accelerazione AI, dato che “Strix Point” è progettato principalmente per PC AI pronti per Microsoft Copilot+, ed è possibile che AVX512 e AVX-VNNI vengano eseguiti su un percorso dati a 256-bit con doppia pompata, similmente a quanto avviene su “Zen 4”, e questo potrebbe comportare vantaggi in termini di performance/Watt, rilevanti per le piattaforme mobile.

Sembra che AMD non abbia disabilitato una funzione fisicamente disponibile, ma piuttosto sviluppato una variante dei core “Zen 5” e “Zen 5c” che manca fisicamente dei percorsi dati a 512-bit. Clark ha spiegato: “E si ottiene il vantaggio di area per poter scalare un po’ di più”, indicando che i core “Zen 5” e “Zen 5c” su “Strix Point” sono fisicamente più piccoli rispetto a quelli sul CCD da 4 nm “Eldora” a 8 core, utilizzato in “Granite Ridge” e in alcuni modelli chiave dei prossimi processori server EPYC “Turin” di quinta generazione.

Fonte: TechPowerUp