AMD Zen 5: nuovi dettagli sulle CPU mobile ''Strix Halo''

19 aprile 2024

1713529245416

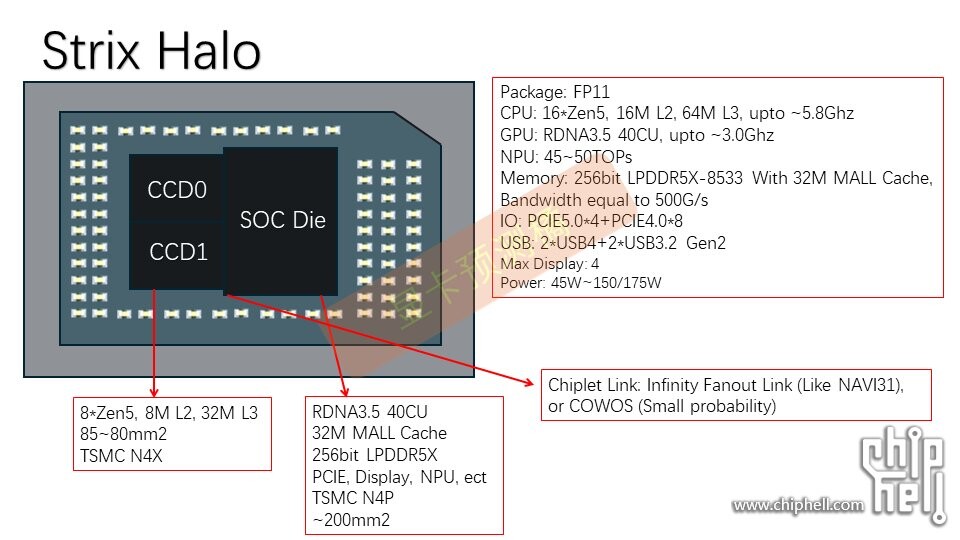

Sul forum cinese ChipHell sono apparse delle immagini sui nuovi processori mobile "Strix Halo" di AMD, una categoria a sé stante diversa dalle attuali generazioni "Hawk Point" e "Phoenix", pronta a rivaleggiare con competitor quali i processori M3 Max e M3 Pro di Apple ma, soprattutto, ad offrire esperienze di gioco paragonabili alle GPU discrete in un fattore di forma ultraportatile.

Il silicio di “Strix Halo” è un processore basato su chiplet, decisamente diverso da “Fire Range”, che rappresenta in sostanza una versione BGA del processore desktop “Granite Ridge”: è la stessa combinazione di uno o due CCD “Zen 5” che dialogano con un die di I/O client, ed è destinato ai notebook del segmento performance-thru-enthusiast. I chip “Strix Halo”, invece, utilizzano gli stessi uno o due CCD “Zen 5”, ma con un SoC di grandi dimensioni dotato di una iGPU sovradimensionata e di controller di memoria LPDDR5X a 256 bit non presenti sul cIOD.

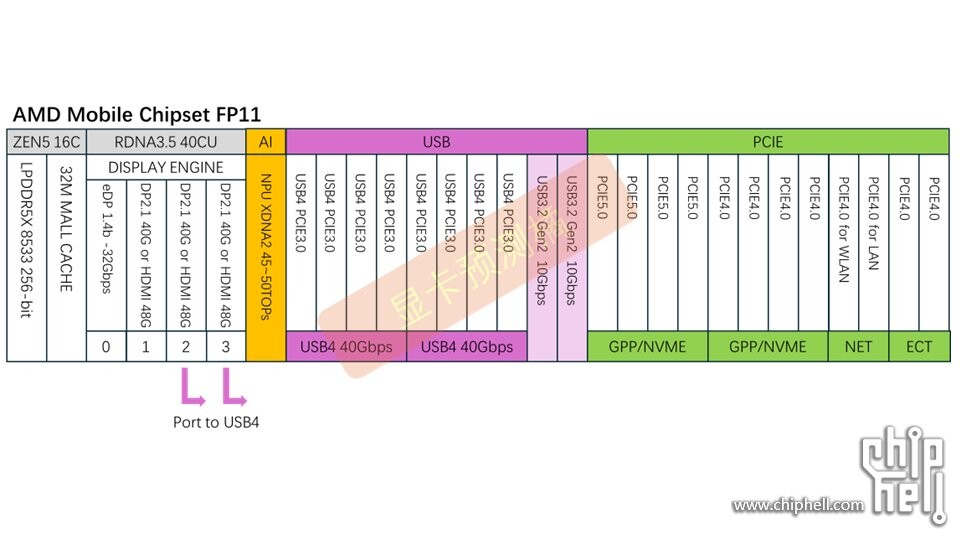

La iGPU di “Strix Halo”, basata sull’architettura grafica RDNA 3+, dispone di ben 40 unità di calcolo RDNA, 2.560 stream processor, 80 acceleratori AI, 40 acceleratori Ray, 160 TMU ed un numero imprecisato di ROP (almeno 64). Il tutto per un clock in grado di raggiungere quota 3,00 GHz.

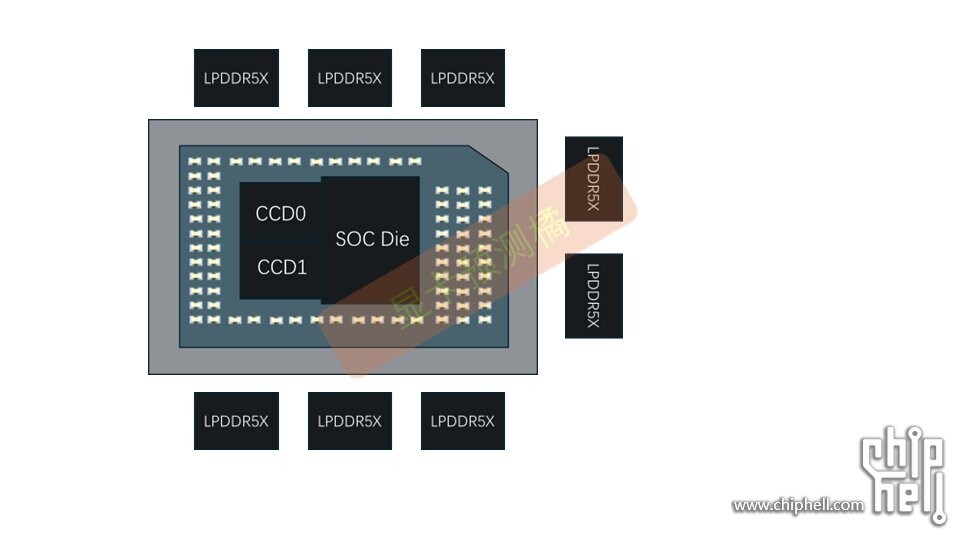

La grafica è un’applicazione estremamente sensibile alla memoria e per questo AMD utilizza un’interfaccia di memoria LPDDR5X-8533 a 256 bit (quad-channel o octa-subchannel), per un’effettiva larghezza di banda in cache di circa 500 GB/s. I controller di memoria sono protetti da una cache L4 da 32 MB situata sul die del SoC. Per quanto riguarda la gerarchia della cache, i CCD (core della CPU) possono trattarla come una cache vittima, mentre la iGPU la tratta come una cache L2 (simile alla Infinite Cache presente nelle GPU discrete RDNA 3). Inoltre, c’è anche una NPU sul SoC, che dovrebbe essere lo stesso modello presente nei processori “Strix Point”, con prestazioni di circa 45-50 AI TOPS, ed è basata sull’architettura XDNA 2 sviluppata dal team Xilinx di AMD.

L’I/O del SoC di “Strix Halo” dispone di 12 linee PCIe Gen 5 - 4 verso uno slot M.2 NVMe ed 8 per una GPU discreta (se presente), anche se queste possono essere utilizzate per collegare qualsiasi dispositivo PCIe, compresi gli slot M.2 aggiuntivi. Sono inoltre integrate USB4 da 40 Gbps e USB 3.2 Gen 2 da 20 Gbps.

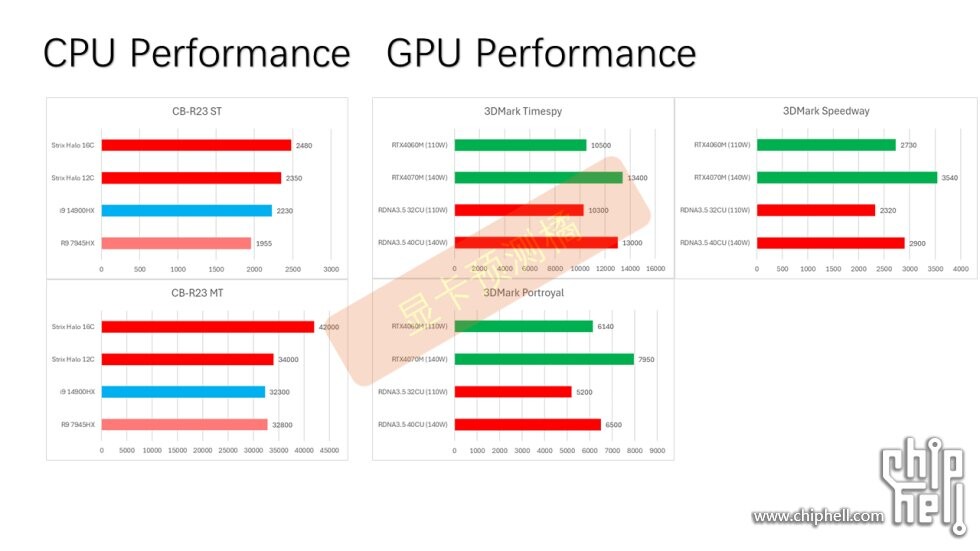

Parlando di prestazioni, le performance lato CPU saranno simili a quelle di “Fire Range”: sono disponibili fino a 16 core CPU “Zen 5”, con 32 MB di cache L3 per ogni CCD, o 64 MB di cache L3 totale della CPU. I CCD sono collegati al die del SoC tramite IFOP (Infinity Fabric over package) convenzionale, proprio come “Fire Range” e “Granite Ridge”. Ma c’è la possibilità che AMD utilizzi collegamenti Infinity Fanout come in alcune delle sue GPU discrete RDNA 3 basate su chiplet. Le prestazioni della iGPU, invece, stando ai rumor riportati, potrebbero essere al livello disoluzioni come le le GeForce RTX 4060M e RTX 4070M di NVIDIA.

Fonti: TechPowerUp, ChipHell Forums